[Total No. of Printed Pages: 3

Roll No .....

## EC-6004 (CBGS) B.E. VI Semester

Examination, May 2018

## Choice Based Grading System (CBGS) VLSI Circuits and Systems

Time: Three Hours

Maximum Marks: 70

Note: i) Attempt any five questions.

- ii) All questions carry equal marks.

- iii) Assume any missing data.

- a) Implement 2×1 MUX using 4 CMOS transistor.

- b) Implement 3-inputs CMOS NAND gates and explain its operations.

- a) Design a modulo-8 binary counter. Use T flip flops in your realization.

- b) A sequential circuit has four flip flops A, B, C, D and input x. It is described by the following state equations.

$$A(tH) = A'B'CDx + A'B'Cx + ACDx' + AC'D'x'$$

B(tH) = A

C(tH) = B

D(tH) = C

Design the sequential circuit described by the above state equation using J-K flip flop. 7

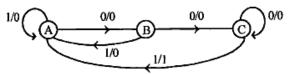

3. a) Construct the state diagram for a MOORE circuit from the following MERLY circuit.

b) The function

f(w, x, y, z) = w'x'z' + wx'z + w'yz + wyz'

Can be decomposed to farm F[g(w, z), x, y].

7

7

Determine the functions F and g.

a) What do you understand by minimization of incompletely specified machines.

b) Describe second state assignments in sequential machine.

a) What are various ways to assign the binary values to the state variable.

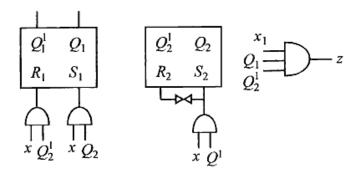

b) Construct a flow table for the following network.

[3]

- 6. a) Find the hazard free realization of the following function  $F(A, B, C, D) = \Sigma_m (0, 2, 6, 7, 8, 10, 12, 13)$  7

- b) What is the fundamental concept of hardware/firmware algorithm? Explain.

- 7. a) Draw the ASM chart for

7

- i) AND Gate

- ii) SR flip-flop

- b) Implement the following Boolean functions using a suitable PAL

- i)  $w(A, B, C, D) = \Sigma_m(1, 3, 4, 6, 9, 11, 12, 14)$

- ii)  $z(A, B, C, D) = \Sigma_m(2, 3, 8, 9, 12, 13)$

- 8. Write short notes on:

14

- a) GAL

- b) Fault diagnosis

- c) PLA