| Name :                    |                                           |

|---------------------------|-------------------------------------------|

| Roll No. :                | As Annual (VE) same bulge 3 and Excellent |

| Invigilator's Signature : |                                           |

## CS / B.TECH (ECE) / SEM-4 / EC-402 / 2011

# 2011

# DIGITAL ELECTRONIC CIRCUITS

Time Allotted : 3 Hours

Full Marks: 70

The figures in the margin indicate full marks. Candidates are required to give their answers in their own words as far as practicable.

## **GROUP - A**

# (Multiple Choice Type Questions)

1. Choose the correct alternatives for any *ten* of the following :

$10 \times 1 = 10$

i) The Excess-3 representation of decimal 59 is

| a) | 01100010 | b) | 00111110 |

|----|----------|----|----------|

|----|----------|----|----------|

c) 10001100 d) none of these.

ii) The number of full address required to construct an *m*-bit parallel adder is

- a) m/2 b) m-2

- c) m d) m + 1.

4053

[ Turn over

c) 20 ns d) none of these.

[ Turn over

CS / B.TECH (ECE) / SEM-4 / EC-402 / 2011

- xi) A two-input EX-OR gate can be used as an inverter when one of its inputs is kept at logic

- a) 0 b) 1

- c) either 0 or 1 d) none of these.

- xii) If the resolution of a D/A converter is approximately 0.4% of its full scale range, it is

- a) an 8-bit converter b) a 10-bit converter

- c) a 12-bit converter d) a 16-bit converter.

#### **GROUP – B**

## (Short Answer Type Questions)

Answer any *three* of the following.  $3 \times 5 = 15$

- Design a Full Adder circuit using a decoder and other necessary logic gates. Assume that the decoder has all active low outputs.

- 3. Design a S-R flip-flop with the help of J-K flip-flop. 5

- 4. Implement a 16:1 MUX by using 4 : 1 MUX only. 5

#### 4053

# CS / B.TECH (ECE) / SEM-4 / EC

- 5. a) Distinguish between synchronous and Asynchronous counters.

- b) Calculate the frequency of 4-bit ripple counter, if the period of waveform at the last flip-flop is 64 microsecond.

- 6. Design a Binary to Gray code converter using PROM. 5

#### **GROUP – C**

#### (Long Answer Type Questions)

Answer any *three* of the following.  $3 \times 15 = 45$

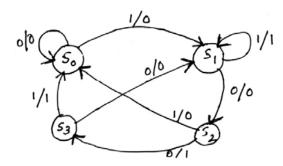

7. a) Design a sequential circuit that implements the following state diagram. (Use D flip-flop) 10

b) Implement the following Boolean function using8:1 MUX:

5

$$F(A, B, C, D) = \sum m(0, 7, 8, 9, 10, 11, 15).$$

5

4053

[ Turn over

D11

- 8. a) Design a MOD-6 synchronous up-counter usin J-K flip-flops.

- b) Implement the following function using  $3 \times 4 \times 2$  PLA :  $F_1(A, B, C) = \sum m(3, 5, 6, 7) F_2(A, B, C) = \sum (0, 2, 4, 7).$  8

- 9. a) Simplify the following function in SOP form using Quine *MC* Cluskey method :

$$F(A, B, C, D) = \sum m(0, 1, 4, 7, 9, 11, 13, 15) + \sum d(3, 5).$$

- b) Describe the operation of a two-input NAND gate constructed with CMOS. 6

- 10. a) Design a combinational circuit for Excess-3 code to BCD conversion using minimum number of logic gates.

9

- b) Describe the principle of operation of successive Approximation type A/D converter. 6

- 4053

- a) 4-bit magnitude comparator

- b) Bi-directional shift register

- c) PAL

- d) Master-slave J-K flip-flop

- e) EEPROM.

\_\_\_\_\_

[ Turn over