## First / Second Semester B.E. Degree Examination, June-July 2009 Basic Electronics

| lime: 3 hrs. | - · |                |

|--------------|-----|----------------|

|              |     | Max. Marks:100 |

Note: 1. Answer any Five full question, choosing at least two from each part.

2. Answer all objectives type questions only in OMR sheet page 5 of the Answer Booklet.

3. Answer to the objective type questions on sheets other than OMR will not be valued

(08 Marks)

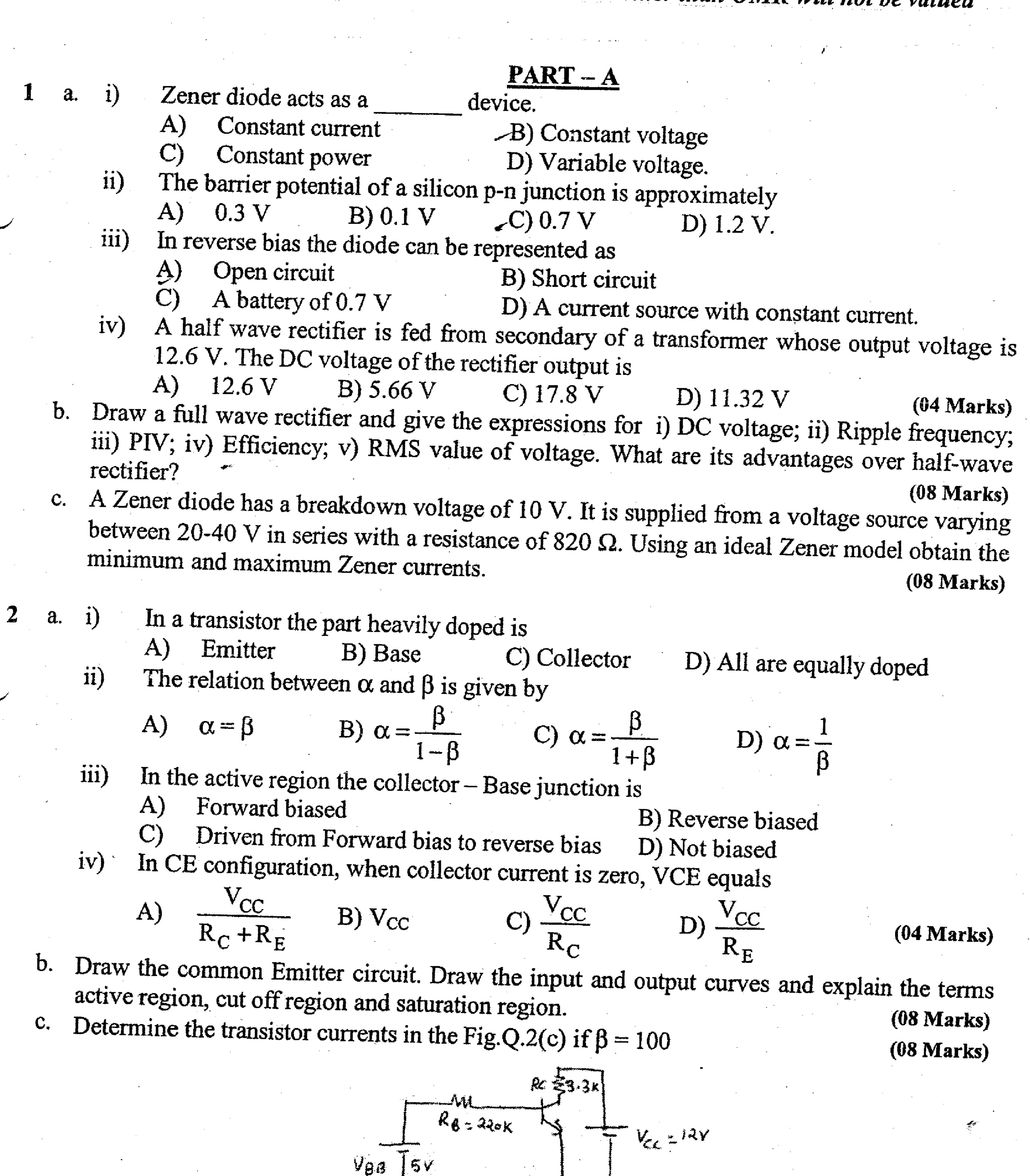

When used as a switch the transistor operates in Active region B) Saturation and cut off C) Cut off region D) Active and saturation. When used as an amplifier the transistor operates in 11) Active region B) Saturation region C) Cut off region D) Can be in any of them Even with sinusoidal base current we get non-sinusoidal collector current in common emitter configuration because of B) Large resistance of signal source Noise introduced in base current Large input resistance of transistor D) Non parallel output characteristics The stability factor S is the rate of change of collector current with iv) Base current B) Reverse saturation current C) Emitter current D) VCC. (04 Marks) b. What is the meaning of transistor biasing? Draw a neat sketch to explain the base biasing of a transistor in CE mode. What is its stability factor S? (08 Marks) c. Draw the DC load line for the voltage-divider biasing circuit shown in Fig.Q.3(c). Find the collector current and the Q point. (08 Marks) -+ VCC = 3eV. 3×v \$6.8Ks ZIKIL 75.0 A Fig.Q.3(c). device The SCR is a C) PNPN D) PNN B) PNP A relaxation oscillator uses D) BJT B) SCR MOSFET controlled device An FET is a iii) C) Current B) Power D) Doping Voltage The gate current in a JFET is 1V) Very large B) Very small C) Significant D) Depends on the input voltage. (04 Marks) b. Draw the structure and symbol of an SCR. Explain its operation and V-I characteristics. (08 Marks) c. Explain the construction and working of an UJT. (08 Marks) PART – B with negative feedback The stability of an amplifier B) Deteriorates Improves C) is not affected D) Depends on amount of negative feedback The Barkhausen criterion states that 11) B)  $A = \frac{1}{0}$ C)  $A\beta = 1$ D)  $A\beta = 0$ .  $A) \quad A = B$ feedback In an oscillator we use B) Negative C) Neither D) Unity gain Positive The input capacitor in a CE amplifier blocks B) DC component A) AC signal D) Noise of a particular frequency C) Both AC and DC (04 Marks) Draw a neat circuit diagram of Hartley's oscillator and explain its working. What is the frequency of oscillations? (08 Marks)

c. Design a Colpitt's oscillator for a frequency of oscillation of 100 kHz.

(06 Marks)

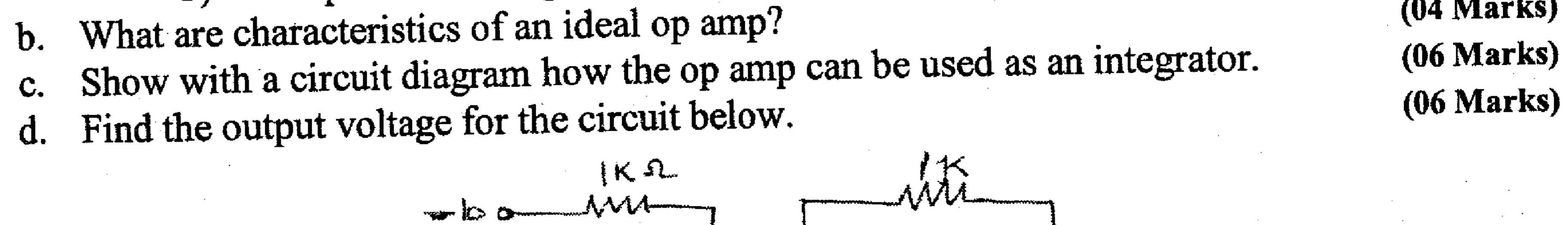

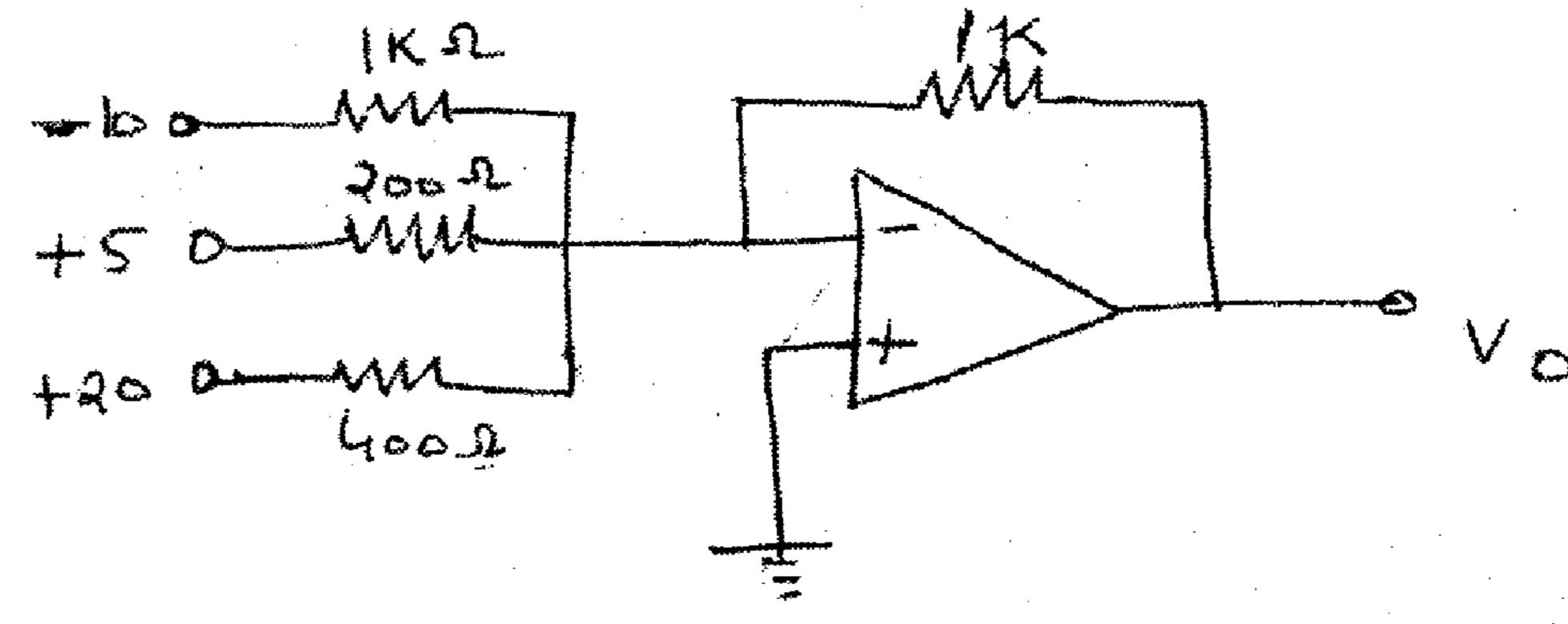

amplifier The op amp is basically a B) Differential Positive feedback D) Common – signal C) Common emitter In an inverting amplifier,  $R_1 = 1$ K and  $R_f = 2$ K. If input voltage is 2V, output voltage D) -4V The CMMR should be iii) B) Much larger than unity Close to unity D) Much smaller then unity Zero When both the inputs of op amp are grounded, the voltage across the output is called iv) B) Output grounded voltage Output off set voltage (04 Marks) D) Output common voltage Output bias voltage (04 Marks)

- The 2'S complement of 1100110 is B) 0011010 0011001 The BCD representation of decimal 10 is 111) D) 10100000 B) 00001001 C) 00010000 The binary of  $(A5)_{16}$  is D) 10100011 (04 Marks) C) 10100101 B) 00100101 Draw the block diagram of a super hetrodyne AM receiver and explain the function of each (08 Marks) block. c. i) Convert (10110011010)<sub>2</sub> into octal, decimal and hexadecimal; ii) Subtract using 2'S (08 Marks)

- complement  $(15-7)_{10}$ . A + AB =Universal gate is ii) D) NAND C) OR B) AND iii) If x + 1 = 1 and  $x \cdot 1 = 0$ , then x is D) Situation can never be true. C) Could be 0 or 1 The output is high only when both inputs are zero to a gate. The gate is (04 Marks) D) NAND. C) OR B) NOR (06 Marks) Draw a full adder circuit with the truth table. (04 Marks)

- c. Simplify ABC + ABC + ABC.

d. Implement OR and AND gates using NOR gates.