D: PH (April Exam) 198

Con. 6398-13.

**GS-6183**

(3 Hours)

Total Marks: 100

N.B. (1) Question No. 1 is compulsory.

- (2) Answer any four out of remaining six questions.

- (3) Assume any suitable data wherever required.

- 1. (a) Draw and explain positive clamper circuit.

5

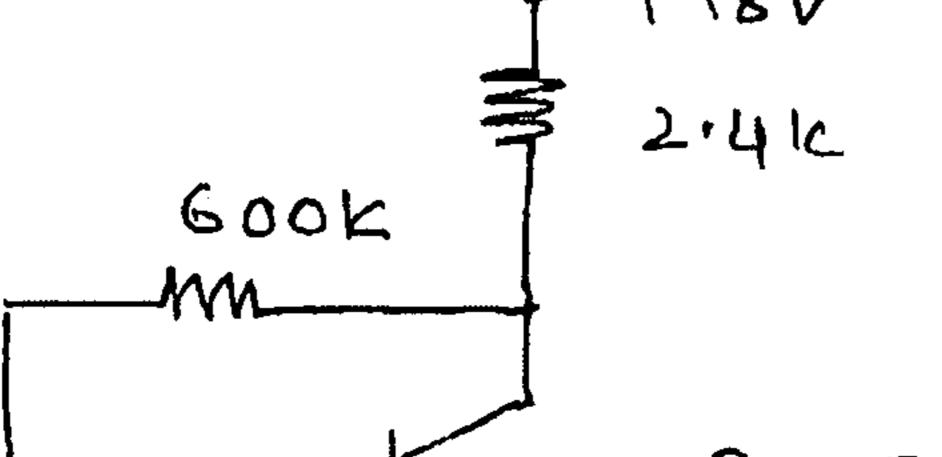

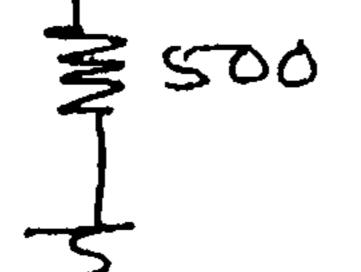

(b) Calculate D.C. collector current IC and voltage V<sub>CE</sub> for given circuit :-

\_\_\_

B=75

(c) Explain bias stabilization in BJT.

5

(d) Derive the condition for zero temperature drift biasing of FET.

5

2. (a) A Fullwave rectifier employing a bridge rectifier using four diodes rectifies 230 V/50 H<sub>z</sub>, mains and supplies 200 V, 0-100 mA to a resistive load employing a filter to give ripple factor of 0.05. Calculate the specifications of the diodes and filter component if the filter used is L & LC filter.

10

(b) Explain the operation of fullwave rectifier and draw the output waveform for  $v_{Ldc}$  and  $I_{Ldc}$ .

10

3. (a) Design a single stage BJT CE amplifier for the following requirements:

15

$$A_v \ge 70$$

,  $Z_i \ge 2.7 \text{ k}\Omega$ ,  $V_O(\text{rms}) = 4.5 \text{ V}$

S = +10.

(b) Determine  $A_v$ ,  $Z_i$ ,  $Z_o$  for design circuit.

5

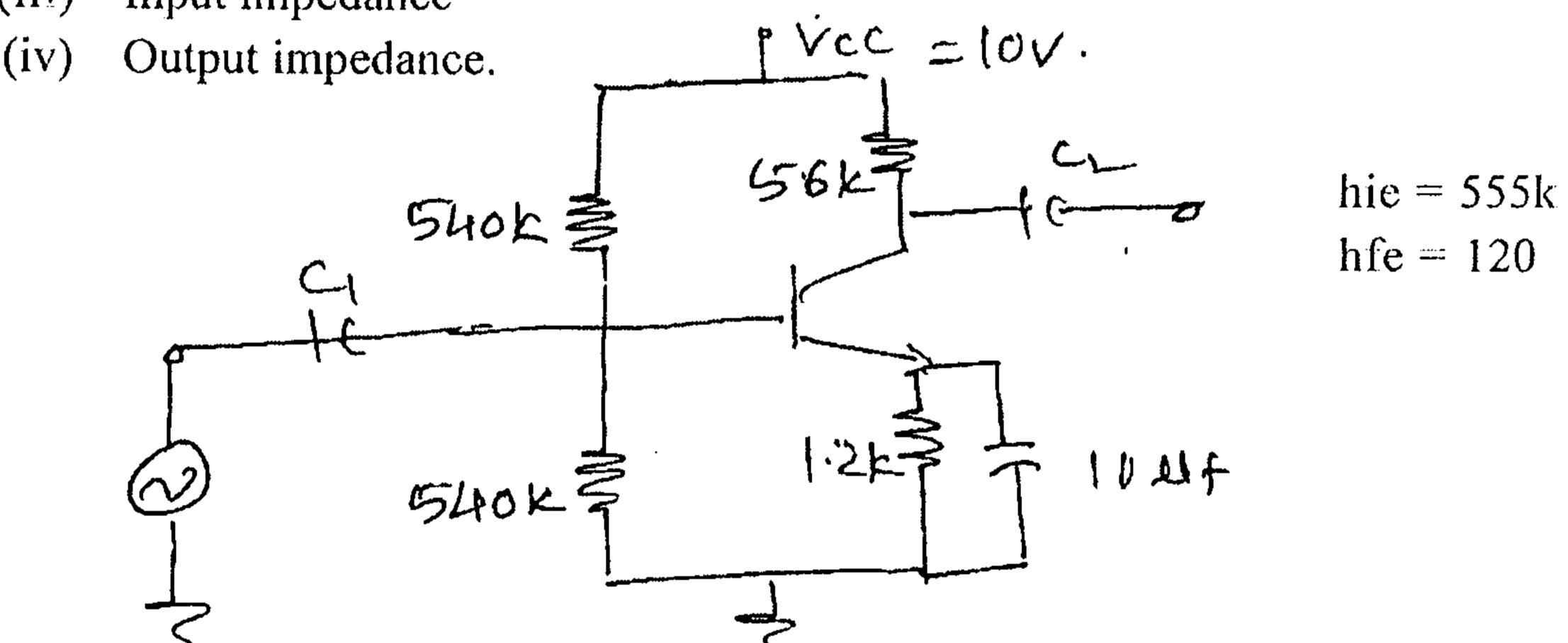

4. (a) For the circuit shown in figure determine, when RE bypass and unbypassed:

15

- (i) Voltage gain A<sub>v</sub>

- (ii) Current gain A<sub>1</sub>

- (iii) Input impedance

(b) Explain hybrid model of BJT

5

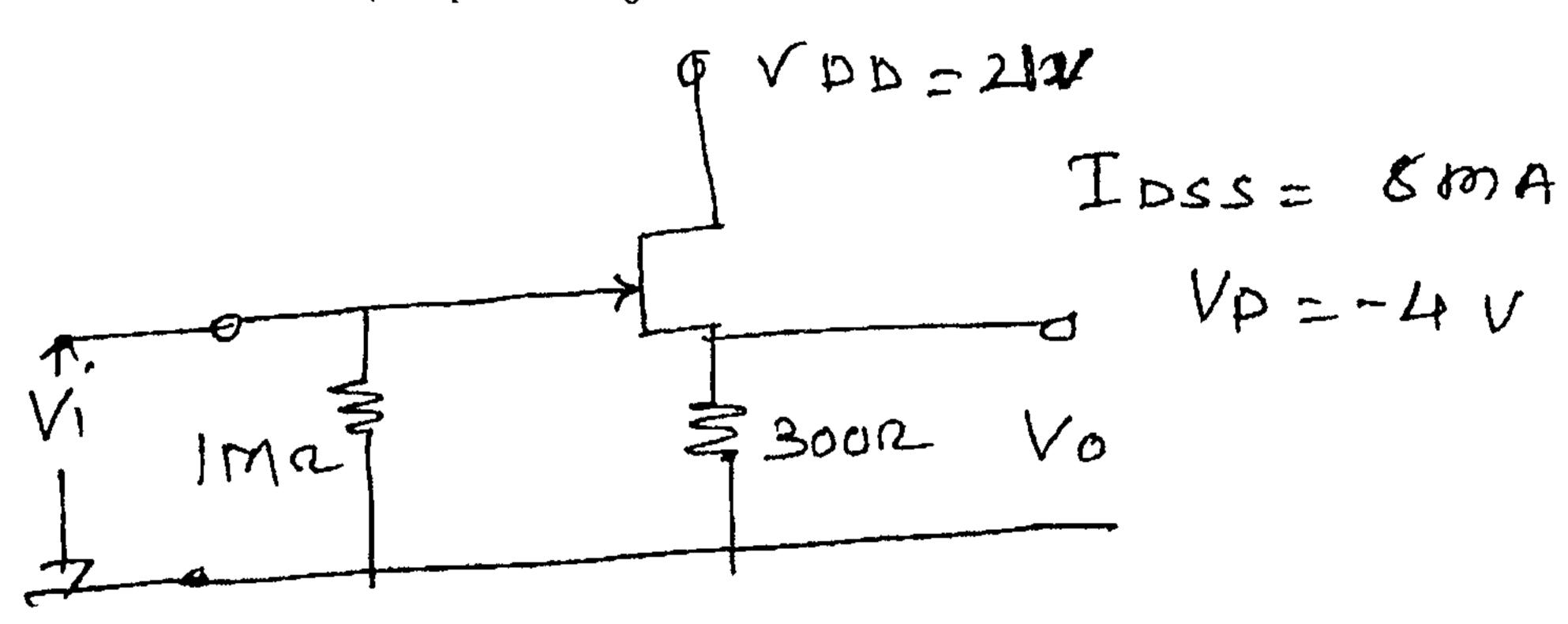

5. (a) Determine A<sub>v</sub>, R<sub>i</sub>, and R<sub>o</sub> for the circuit shown in figure.

10

(b) Draw neat diagram of CS amplifier with voltage divider (Bypassed Rs) configuration. Derive the expression for  $Z_i$ ,  $Z_o$  and  $A_v$ .