# 8086

**MICROPROCESSOR**

## **IMPORTANT FEATURES OF 8086:**

#### 1) Buses:

Address Bus: 8086 has a **20-bit address bus**, hence it can access 2<sup>20</sup> Byte memory i.e. **1MB**. The **address range** for this memory is **00000H** ... **FFFFFH**.

<u>Data Bus</u>: 8086 has a **16-bit data bus** i.e. it can access 16 bit data in one operation. Its ALU and internal data registers are also 16-bit. **Hence** 8086 is called as a **16-bit**  $\mu$ **P**.

<u>Control Bus</u>: The control bus carries the signals responsible for performing various operations such as <u>RD</u>, <u>WR</u> etc.

2) 8086 supports Pipelining.

It is the process of "Fetching the next instruction, while executing the current instruction". Pipelining improves performance of the system.

- 3) 8086 has 2 Operating Modes.

- i. Minimum Mode ... here 8086 is the only processor in the system (uni-processor).

- ii. Maximum Mode ... 8086 with other processors like 8087-NDP/8089-IOP etc. Maximum mode is intended for multiprocessor configuration.

- 4) 8086 provides Memory Banks.

The entire memory of 1 MB is **divided into 2 banks of 512KB each**, in order to transfer bits in 1 cycle. The banks are called **Lower Bank** (even) **and Higher Bank** (odd).

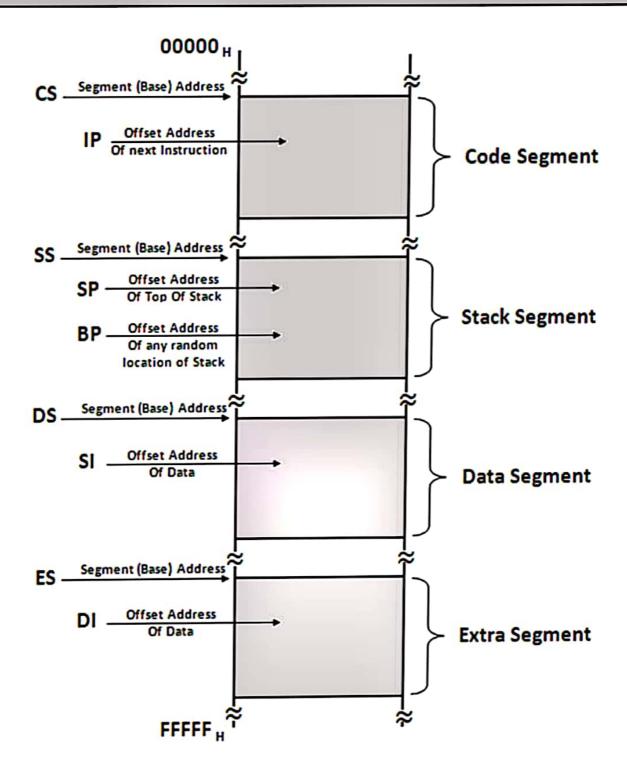

- 5) 8086 supports Memory Segmentation. Segmentation means dividing the memory into logical components. Here the memory is divided into 4 segments: Code, Stack, Data and Extra Segment.

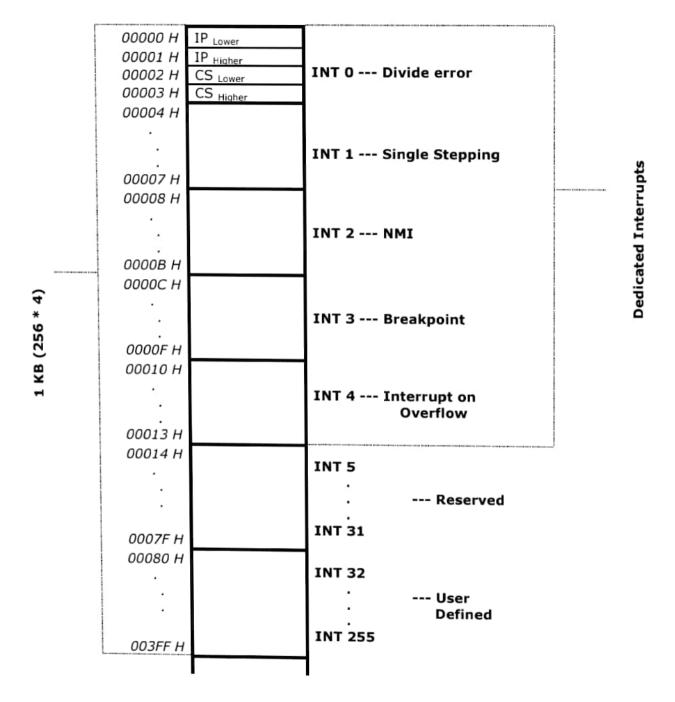

- 6) 8086 has 256 interrupts.

The ISR addresses for these interrupts are stored in the IVT (Interrupt Vector Table).

- 7) 8086 has a **16-bit IO address** : it can access  $2^{16}$  **IO ports** ( $2^{16}$  = 65536 i.e. 64K IO Ports).

# **ARCHITECTURE OF 8086**

As 8086 does 2-stage pipelining, its architecture is divided into two units:

- 1. Bus Interface Unit (BIU)

- 2. Execution Unit (EU)

## **BUS INTERFACE UNIT (BIU)**

- It provides the interface of 8086 to other devices.

- 2. It operates w.r.t. Bus cycles .

This means it performs various machine cycles such as Mem Read, IO Write etc to transfer data with Memory and I/O devices.

- 3. It performs the following functions:

- a) It generates the 20-bit physical address for memory access.

- b) Fetches Instruction from memory.

- c) Transfers data to and from the memory and IO.

- d) Supports Pipelining using the 6-byte instruction queue.

## The main components of the BIU are as follows:

## a) **SEGMENT REGISTERS**:

## 1) CS Register

CS holds the base (Segment) address for the Code Segment.

All programs are stored in the Code Segment.

It is multiplied by 10H (16<sub>d</sub>), to give the 20-bit physical address of the Code Segment.

Eg: If CS = 4321H then CS × 10H = 43210H → Starting address of Code Segment.

CS register cannot be modified by executing any instruction except branch instructions

#### 2) DS Register

DS holds the base (Segment) address for the Data Segment.

It is multiplied by 10H (16<sub>d</sub>), to give the 20-bit physical address of the Data Segment.

Eg: If DS = 4321H then DS × 10H = 43210H → Starting address of Data Segment.

## 3) SS Register

SS holds the base (Segment) address for the Stack Segment.

It is multiplied by 10H (16d), to give the 20-bit physical address of the Stack Segment.

Eg: If SS = 4321H then SS × 10H = 43210H → Starting address of Stack Segment.

#### 4) ES Register

ES holds the base (Segment) address for the Extra Segment.

It is multiplied by 10H (16<sub>d</sub>), to give the 20-bit physical address of the Extra Segment.

Eg: If ES = 4321H then ES × 10H = 43210H → Starting address of Extra Segment.

## b) Instruction Pointer (IP register)

It is a 16=bit register.

It holds offset of the next instruction in the Code Segment.

Address of the next instruction is calculated as CS x 10H + IP.

IP is incremented after every instruction byte is fetched.

IP gets a new value whenever a branch occurs.

#### c) Address Generation Circuit

The BIU has a **Physical Address Generation Circuit.** It generates the 20-bit physical address using Segment and Offest addresses using the formula:

## Physical address = Segment Address x 10h + Offset Address

Viva Question: Explain the real procedure to obtain the Physical Address?

The Segment address is left shifted by 4 positions, this multiplies the number by 16 (i.e. 10h) and then the offset address is added.

Eg: If Segment address is 1234h and Offset address is 0005h, then the physical address (12345h) is calculated as follows:  $1234h = (0001\ 0010\ 0011\ 0100)_{binary}$

Left shift by four positions and we get (0001 0010 0011 0100 0000) i.e. 12340h

Now add (0000 0000 0000 0101)<sub>binary</sub> i.e. 0005h and we get (0001 0010 0011 0100 0101)<sub>binary</sub> i.e. 12345h.

## d) 6-Byte Pre-Fetch Queue {Pipelining - 4m}

It is a 6-byte FIFO RAM used to implement Pipelining.

Fetching the next instruction while executing the current instruction is called Pipelining.

**BIU fetches** the next "**six instruction-bytes**" from the Code Segment and stores it into the queue. Execution Unit (EU) removes instructions from the queue and executes them.

The queue is refilled when atleast two bytes are empty as 8086 has a 16-bit data bus. Pipelining increases the efficiency of the  $\mu P$ .

Pipelining fails when a branch occurs, as the pre-fetched instructions are no longer useful.

Hence as soon as 8086 detects a branch operation, it clears/discards the entire queue. Now, the next six bytes from the new location (branch address) are fetched and stored in the queue and Pipelining continues.

## **NON-PIPELINED PROCESSOR EG: 8085**

## **PIPELINED PROCESSOR EG: 8086**

## **Execution Unit (EU)**

- 1. It fetches instructions from the Queue in BIU, decodes and executes them.

- 2. It performs arithmetic, logoc and internal data transfer operations.

- 3. It sends request signals to the BIU to access the external module.

- 4. It operates w.r.t. T-States (clock cycles). © For doubts contact Bharat Sir on 98204 08217

## The main components of the EU are as follows:

## a) General Purpose Registers

8086 has four 16-bit general-purpose registers AX, BX, CX and DX. These are available to the programmer, for storing values during programs. Each of these can be divided into two 8-bit registers such as AH, AL; BH, BL; etc. Beside their general use, these registers also have some specific functions.

## AX Register (16-Bits)

It holds operands and results during multiplication and division operations. All IO data transfers using IN and OUT instructions use A reg (AL/AH or AX). It functions as accumulator during string operations.

## BX Register (16-Bits)

Holds the memory address (offset address), in Indirect Addressing modes.

## CX Register (16-Bits)

Holds count for instructions like: Loop, Rotate, Shift and String Operations.

## DX Register (16-Bits)

It is used with AX to hold 32 bit values during Multiplication and Division. It is used to hold the address of the IO Port in indirect IO addressing mode.

## b) Special Purpose Registers

## Stack Pointer (SP 16-Bits)

It is holds offset address of the top of the Stack. Stack is a set of memory locations operating in LIFO manner. Stack is present in the memory in Stack Segment.

SP is used with the SS Reg to calculate physical address for the Stack Segment. It used during instructions like PUSH, POP, CALL, RET etc. During PUSH instruction, SP is decremented by 2 and during POP it is incremented by 2.

## Base Pointer (BP 16-Bits)

BP can hold offset address of any location in the stack segment.

It is used to access random locations of the stack. #Please refer Bharat Sir's Lecture Notes for this ...

## Source Index (SI 16-Bits)

It is normally used to hold the offset address for Data segment but can also be used for other segments using Segment Overriding. It holds offset address of source data in Data Seg, during String Operations.

#### Destination Index (DI 16-Bits)

It is normally used to hold the **offset address** for **Extra segment** but can also be used for other segments using Segment Overriding. It holds **offset address** of **destination** in Extra Seg, during **String Operations**.

#### c) ALU (16-Bits)

It has a 16-bit ALU. It performs 8 and 16-bit arithmetic and logic operations.

## d) Operand Register

It is a 16-bit register used by the control register to hold the operands temporarily. It is **not available** to the Programmer.

e) Instruction Register and Instruction Decoder (Present inside the Control Unit) The EU fetches an opcode from the queue into the Instruction Register. The Instruction Decoder decodes it and sends the information to the control circuit for execution.

## f) Flag Register (16-Bits)

It has 9 Flags.

These flags are of two types: 6-Status (Condition) Flags and 3-Control Flags.

Status flags are affected by the ALU, after every arithmetic or logic operation. They give the status of the current result.

The Control flags are used to control certain operations.

They are changed by the programmer.

## STATUS FLAGS

1) Carry flag (CY)

It is **set** whenever there is a **carry** {or borrow} out of the MSB of a the result (D7 bit for an 8-bit operation D15 bit for a 16-bit operation)

2) Parity Flag (PF)

It is set if the result has even parity.

3) Auxiliary Carry Flag (AC)

It is set if a carry is generated out of the Lower Nibble.

It is used only in 8-bit operations like DAA and DAS.

4) Zero Flag (ZF)

It is set if the result is zero.

5) Sign Flag (SF)

It is set if the MSB of the result is 1.

For signed operations, such a number is treated as -ve.

6) Overflow Flag (OF)

It will be set if the **result of** a **signed operation** is **too large to fit** in the number of bits available to represent it. It can be **checked using** the **instruction INTO** (Interrupt on Overflow). #Please refer Bharat Sir's Lecture Notes for this ...

## **CONTROL FLAGS**

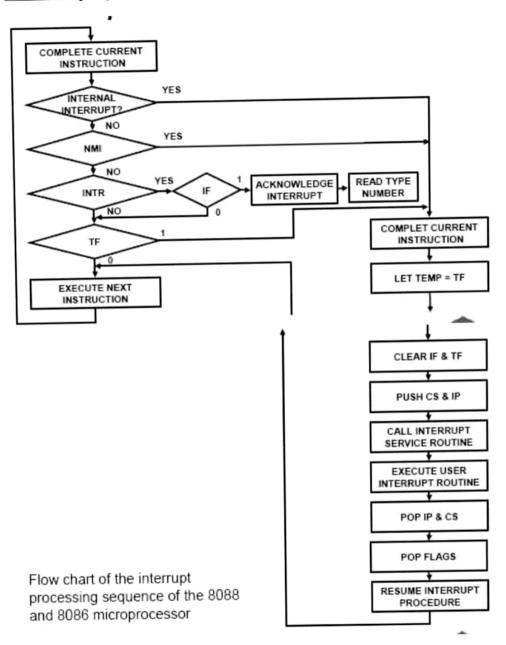

1) Trap Flag (**TF**)

It is used to **set** the Trace Mode i.e. start **Single Stepping Mode**.

Here the  $\mu P$  is interrupted after every instruction so that, the program can be debugged.

2) Interrupt Enable Flag (IF)

It is used to mask (disable) or unmask (enable) the INTR interrupt.

3) Direction Flag (DF)

If this flag is set, SI and DI are in auto-decrementing mode in String Operations.

## **MEMORY SEGMENTATION IN 8086**

## **NEED FOR SEGMENTATION / CONCEPT OF SEGMENTATION**

- 1) Segmentation means dividing the memory into logically different parts called segments.

- 2) 8086 has a **20-bit address bus**, hence it can access 2<sup>20</sup> Bytes i.e. **1MB** memory.

- 3) But this also means that Physical address will now be 20 bit.

- It is not possible to work with a 20 bit address as it is not a byte compatible number.

(20 bits is two and a half bytes).

- 5) To avoid working with this incompatible number, we create a virtual model of the memory.

- 6) Here the memory is divided into 4 segments: Code, Stack Data and Extra.

- 7) The max size of a segment is 64KB and the minimum size is 16 bytes.

- 8) Now programmer can access each location with a VIRTUAL ADDRESS.

- 9) The Virtual Address is a combination of Segment Address and Offset Address.

- 10) Segment Address indicates where the segment is located in the memory (base address)

- 11) Offset Address gives the offset of the target location within the segment.

- 12) Since both, Segment Address and Offset Address are **16 bits each**, they both are **compatible numbers** and can be easily used by the programmer.

- 13) Moreover, **Segment Address is given only in the beginning** of the program, to initialize the segment. Thereafter, we **only give offset address**.

- 14) Hence we can access 1 MB memory using only a 16 bit offset address for most part of the program. This is the advantage of segmentation.

- 15) Moreover, dividing Code, stack and Data into different segments, makes the memory more organized and prevents accidental overwrites between them.

- 16) The Maximum Size of a segment is 64KB because offset addresses are of 16 bits.  $2^{16} = 64KB$ .

- 17) As max size of a segment is 64KB, programmer can create multiple Code/Stack/Data segments till the entire 1 MB is utilized, but only one of each type will be currently active.

- 18) The physical address is calculated by the microprocessor, using the formula:

#### PHYSICAL ADDRESS = SEGMENT ADDRESS X 10H + OFFSET ADDRESS

- 19) Ex: if Segment Address = 1234H and Offset Address is 0005H then Physical Address =  $1234H \times 10H + 0005H = 12345H$

- 20) This formula automatically ensures that the minimum size of a segment is 10H bytes (10H = 16 Bytes).

## Code Segment

This segment is used to hold the **program** to be executed.

Instruction are fetched from the Code Segment.

CS register holds the 16-bit base address for this segment.

IP register (Instruction Pointer) holds the 16-bit offset address.

## **Data Segment**

This segment is used to hold general data.

This segment also holds the **source** operands during **string** operations.

DS register holds the 16-bit base address for this segment.

BX register is used to hold the 16-bit offset for this segment.

SI register (Source Index) holds the 16-bit offset address during String Operations.

## Stack Segment

This segment holds the **Stack** memory, which operates in LIFO manner.

SS holds its Base address.

SP (Stack Pointer) holds the 16-bit offset address of the Top of the Stack.

BP (Base Pointer) holds the 16-bit offset address during Random Access.

## **Extra Segment**

This segment is used to hold general data

Additionally, this segment is used as the destination during String Operations.

ES holds the Base Address.

**DI** holds the **offset** address during string operations.

## **Advantages of Segmentation:**

- 1) It permits the programmer to access 1MB using only 16-bit address.

- 2) Its divides the memory logically to store Instructions, Data and Stack separately.

## Disadvantage of Segmentation:

1) Although the total memory is 16\*64 KB, at a time only 4\*64 KB memory can be accessed.

## MEMORY BANKING IN 8086

- As 8086 has a 16-bit data bus, it should be able to access 16-bit data in one cycle.

- To do so it needs to read from 2 memory locations, as one memory location carries only one byte.

16-bit data is stored in two consecutive memory locations.

- However, if both these memory locations are in the same memory chip then they cannot be accessed

at the same time, as the address bus of the chip cannot contain two address simultaneously.

- · Hence, the memory of 8086 is divided into two banks each bank provides 8-bits.

- The division is done in such a manner that any two consecutive locations lie in two different chips. Hence each chip contains alternate locations.

- One bank contains all even addresses called the "Even bank", while the other is called "Odd bank" containing all odd addresses.

- Generally for any 16-bit operation, the Even bank provides the lower byte and the ODD bank provides the higher byte. Hence the Even bank is also called the Lower bank and the Odd bank is also called the Higher bank.

#### **1 MB** 512 KB 512 KB Even Bank **Odd Bank** Also called as "Lower bank" Also called as "Higher bank" Address range: Address range: 00000H 00001H 00002H 00003H 00004H 00005H **FFFFEH FEFFFH** Selected when $A_0 = 0$ Selected when BHE = 0

| BHE | Ao | OPERATION                  |  |

|-----|----|----------------------------|--|

| 0   | 0  | R/W 16-bit from both banks |  |

| 0   | 1  | R/W 8-bit from higher bank |  |

| 1   | 0  | R/W 8-bit from lower bank  |  |

| 1   | 1  | No Operation (Idle).       |  |

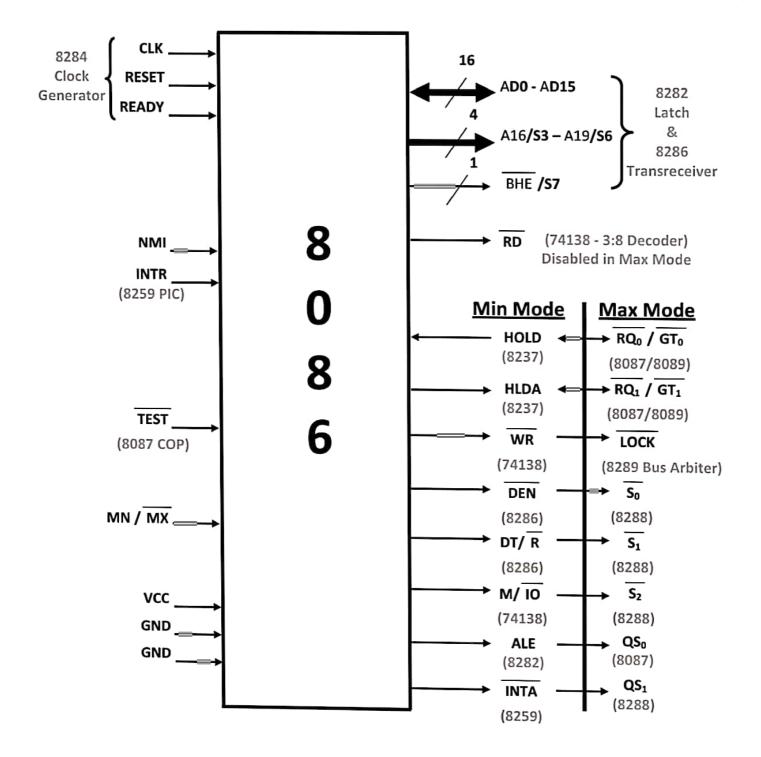

## PIN DIAGRAM OF 8086

# **Machine Cycles**

| S <sub>2</sub> | Sı | So | Bus Cycle / Machine Cycle |

|----------------|----|----|---------------------------|

| 0              | 0  | 0  | INTA Cycle                |

| 0              | 0  | 1  | I/O Read                  |

| 0              | 1  | 0  | I/O Write                 |

| 0              | 1  | 1  | Halt                      |

| 1              | 0  | 0  | Opcode Fetch              |

| 1              | 0  | 1  | Memory Read               |

| 1              | 1  | 0  | Memory Write              |

| 1              | 1  | 1  | Inactive                  |

# **Segment Selection**

| S <sub>4</sub> S <sub>3</sub> | Segment. Selected      |

|-------------------------------|------------------------|

| 0 0                           | Extra Segment          |

| 0 1                           | Stack Segment          |

| 1 0                           | CS/No Segment Selected |

| 1 1                           | Data Segment           |

# **Queue Synchronization**

| QS <sub>1</sub> QS <sub>0</sub> | Queue Operation                              |

|---------------------------------|----------------------------------------------|

| 0 0                             | NOP                                          |

| 0 1                             | Opcode Fetch from queue                      |

| 1 0                             | Queue is Cleared                             |

| 1 1                             | Fetch remaining instruction bytes form queue |

#### **PIN DESCRIPTIONS**

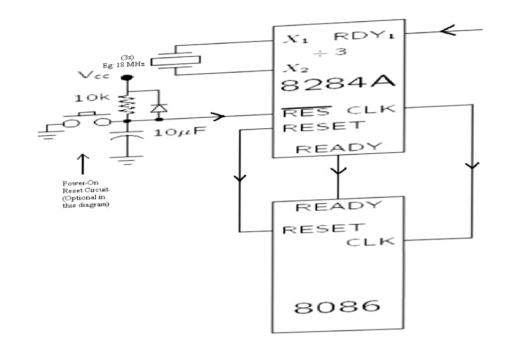

#### CLK

This is the clock-input line. An external clock generator (8284) provides the clock signal. 8086 required single phase, 33% duty cycle, TTL clock signal.

#### RESET

This is the reset input signal. The 8284 Clock generator provides it. It Clears the Flag register and the Instruction Queue. It also Clears the DS, SS, ES and IP registers and Sets the bits of CS register. Hence the reset vector address of 8086 is FFFFOH (as CS = FFFFH and IP = 0000H).

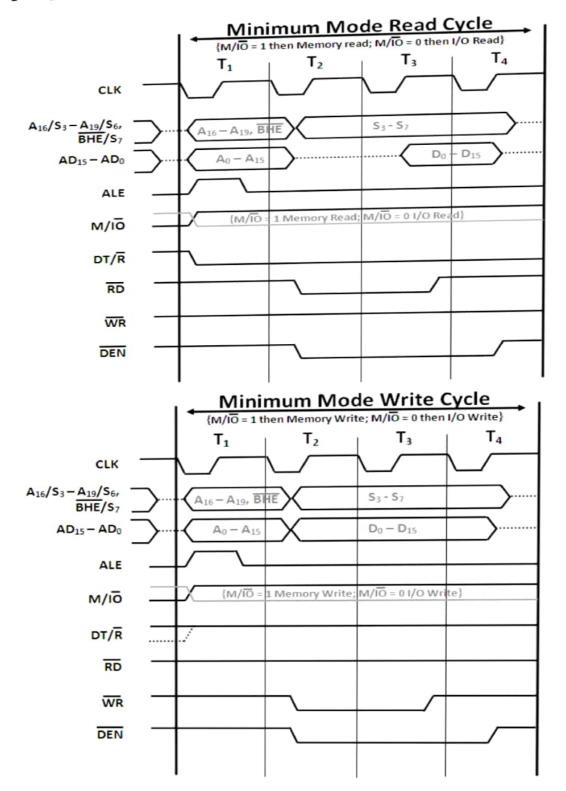

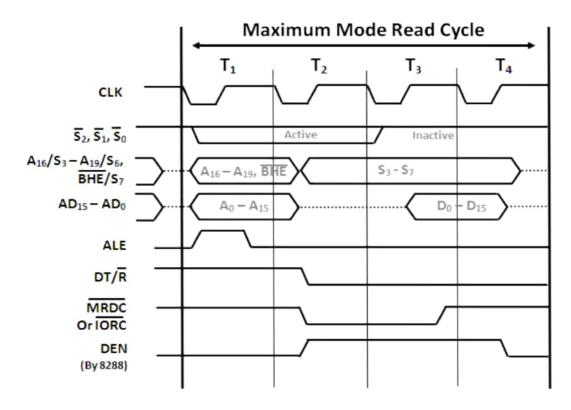

#### READY

This signal is used to synchronize the  $\mu P$  with **slower peripherals**. Devices inform the  $\mu P$  whether they are ready or not.  $\mu P$  **samples** the READY input **during T3 state** of a Machine Cycle If device is Ready it send a "1" on the Ready pin else send a "0". If Ready pin is 0,  $\mu P$  inserts **wait-states** between T3 and T4 and will only come out of Wait state when Ready becomes 1 thereby ensuring that the Device is ready.

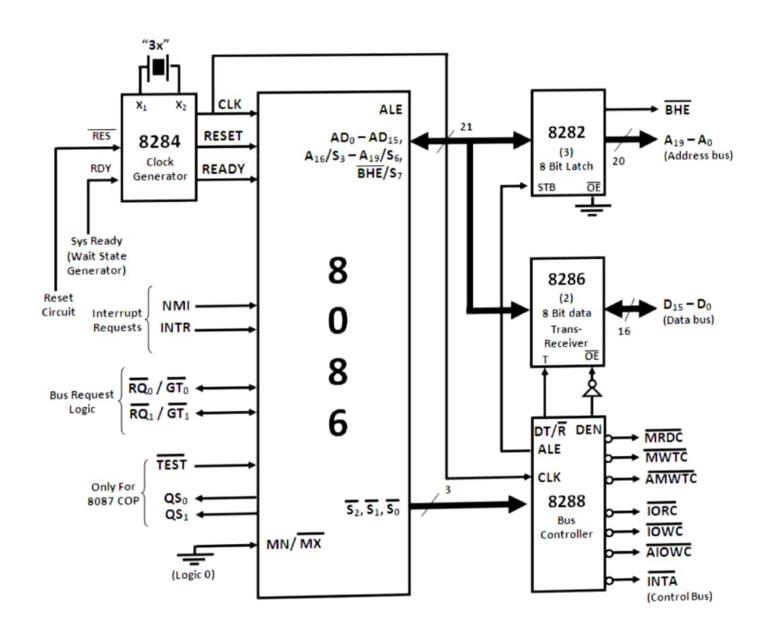

## TEST

It is an active low **input** line dedicated for 8087 Co-processor. In **Maximum Mode** whenever the **Co-Processor** is **busy** it makes this pin HIGH.  $\mu P$  samples the  $\overline{\text{TEST}}$  input only when it encounters the WAIT instruction.

If the  $\overline{\text{TEST}}$  pin is **high**, the  $\mu P$  enters wait state, till  $\overline{\text{TEST}}$  pin becomes low i.e. 8087 is free. In minimum mode it is not used and is connected to ground (VIVA Q).

## · MN/MX

This is an input signal to 8086.

If this signal is **HIGH**, 8086 is in **Minimum** mode i.e. Uni-Processor system. If this signal is **Low**, 8086 is in **Maximum** mode i.e. Multiprocessor system.

#### NMI

This is a non-maskable, edge triggered, high priority interrupt.

On receiving an interrupt on NMI line, the  $\mu P$  executes **INT 2** i.e. and takes control to location 2 x 4 = 00008H in the Interrupt Vector Table (IVT), to get the value for CS ad IP.

#### INTR

This is a maskable, level triggered, low priority interrupt.

On receiving an interrupt on INTR line, the  $\mu P$  executes 2 INTA cycles.

On FIRST INTA pulse, the interrupting device (8259) prepares to send a vector number "N".

On SECOND INTA pulse, the interrupting device (8259 PIC) sends vector number "N" to  $\mu$ P.

Now  $\mu P$  will multiply N x 4 and go to the IVT to obtain the ISR address i.e. values for IP and CS.

## RD

It is an active low output signal. When it is low 8086 reads from memory or IO.

## VCC and GND

Used for power supply. Two grounds are due to the two internal layers in  $\mu P$ .

## AD15 - AD0

It carries  $A_{15}$  -  $A_0$  (address) during T1 of a Machine Cycle when ALE = 1. It carries  $D_{15}$  -  $D_0$  (data) for remaining T-States of a Machine Cycle when ALE = 0.

## A16/S3 - A19/S6

These lines carry ( $A_{16}$  ...  $A_{19}$ ) during T1 of every M/C Cycle. T2 onwards these lines carry the Status signals  $S_3$  ...  $S_6$ .  $S_3$  and  $S_4$  indicate the memory segment currently accessed.  $S_5$  gives the status of the **Interrupt Enable Flag**.  $S_6$  goes **low** when **8086 controls the system bus**.

## BHE /S7

It carries BHE during T1. BHE is used to enable the higher bank.

T2 onwards it carries S7, which is reserved for "further development" @ .

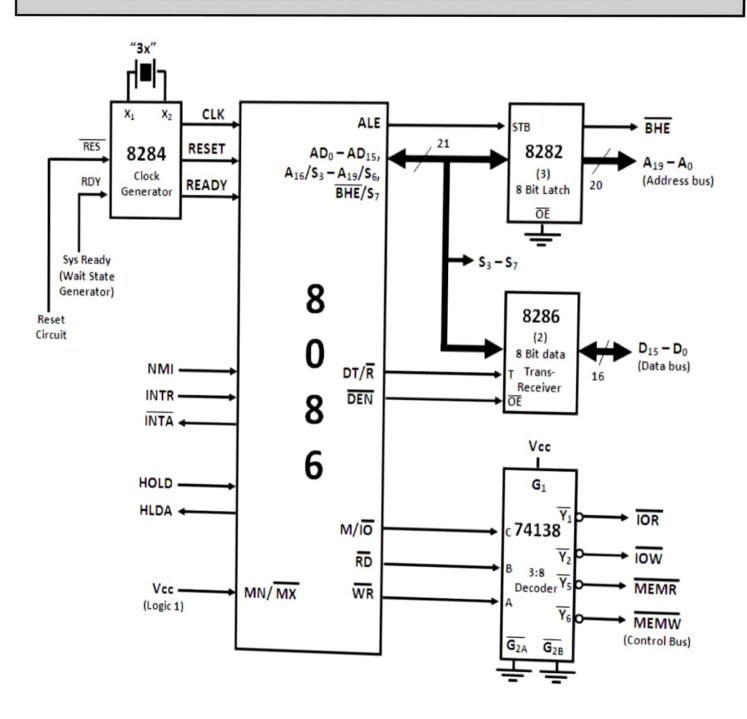

# MIN Mode / Max Mode Signals (10m question --- Important)

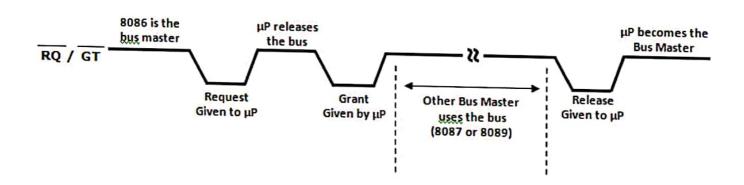

## HOLD --- RQ o/ GT o

In **Minimum** Mode this line carries the **HOLD** input signal.

The **DMA Controller issues** the HOLD signal to request for the system bus.

In response 8086 completes the current bus cycle and releases the system bus.

In Maximum Mode it carries the bi-directional RQ o/ GT o signal (Request/Grant). The external bus master (eg: 8087) sends an active low pulse to request for the sys bus.

In response the 8086 completes the current bus cycle, releases the system bus and sends an active low Grant pulse on the same line to the external bus controller.

8086 gets back the system bus only after external bus master sends an active low release pulse on the same line.

# • HLDA --- RQ 1/ GT 1

In **Minimum** Mode this line carries the **HLDA** signal. This signal is issued by 8086 after releasing the system bus.

In **Maximum** Mode it functions as  $\overline{RQ}_{1}/\overline{GT}_{1}$ , which is the same as  $\overline{RQ}_{0}/\overline{GT}_{0}$  but is of **lower** priority.

## WR --- LOCK

In **Minimum** Mode this line carries the **WR** signal.

It is used with  $M/\overline{10}$  to write to Memory or IO Device.

In Maximum Mode it functions as the LOCK output line.

When this signal is active (i.e. low) the external bus master cannot take control of the system bus. It is activated when 8086 executes an instruction with the LOCK prefix, and remains active till next instruction.

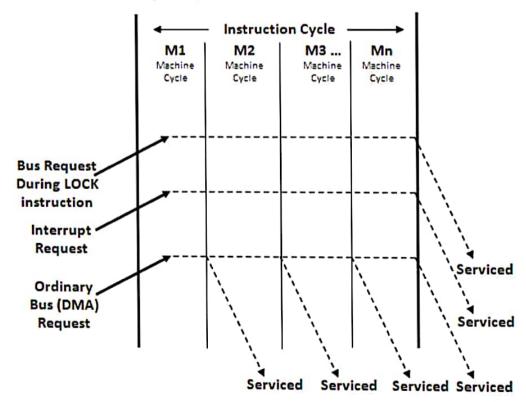

**LOCK Prefix:** Normally a bus request is serviced after the current machine cycle and an interrupt request is serviced after the current instruction cycle.

But if we write LOCK prefix before any instruction, then even if there is a bus request, the bus will be released only after the current instruction. Hence the bus is said to be locked during the instruction.

μΡ will maintain LOCK signal low throughout the instruction to indicate that it is performing an

instruction with LOCK prefix. LOCK signal is given to 8289 Bus Arbiter in Loosely Coupled Systems, to prevent 8289 from releasing the system bus to other bus masters.

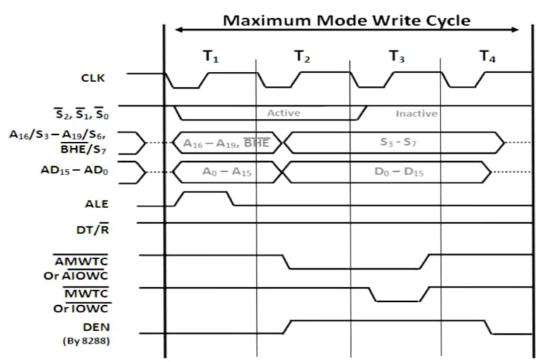

## • DEN --- SO

In Minimum Mode it carries the **DEN** signal

It is used to enable the data transceivers (bi-directional buffers - IC 8286).

In **Maximum** Mode it carries the  $\overline{S_0}$  signal.

In Maximum Mode, Bus Controller (IC 8288) gives the DEN signal.

## • DT/R --- S1

In Minimum Mode it carries the DT/R signal

This signal goes low for a Read operation and high for a write operation.

In **Maximum** Mode it carries the  $\overline{S_1}$  signal.

In Maximum Mode, Bus Controller gives the DT/R signal.

| DEN | DT/R | Action                    |

|-----|------|---------------------------|

| 1   | X    | Transreceiver is disabled |

| 0   | 0    | Receive data              |

| 0   | 1    | Transmit data             |

## • M/ IO --- S2

In **Minimum** Mode it carries the  $M/\overline{10}$  signal, to distinguish between Memory and IO access.

In **Maximum** Mode it carries the  $\overline{S_2}$  signal.

In Maximum Mode  $\overline{S_2}$ ,  $\overline{S_1}$  and  $\overline{S_0}$  are used to generate the appropriate control signal.

| M/ IO | RD | WR | Action       |  |

|-------|----|----|--------------|--|

| 1     | 0  | 1  | Memory Read  |  |

| 1     | 1  | 0  | Memory Write |  |

| 0     | 0  | 1  | I/O Read     |  |

| 0     | 1  | 0  | I/O Write    |  |

## ALE --- QS0

In Minimum Mode it carries the ALE signal, which is used to latch the address.

In Maximum Mode it carries the QSo signal.

It is used with QS1 to indicate the Instruction Queue Status.

In Maximum Mode, Bus Controller gives the ALE signal.

# INTA --- QS1

In **Minimum** Mode it carries the **INTA** signal

It is issued in response to an interrupt on the INTR line.

It is used to read the vector number form the interrupting device.

In Maximum Mode it carries the QS1 signal. © For doubts contact Bharat Sir on 98204 08217

In Maximum Mode, Bus Controller gives the INTA signal.

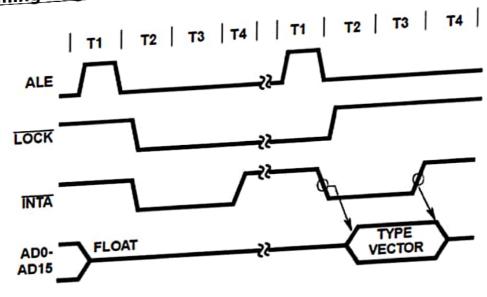

# Timing diagram for 2 back-to-back INTA cycles

- As shown above there are two INTA cycles.

- Each INTA cycle is of 4 T-states

- In the 1st INTA cycle, the interrupting device (8259) starts preparing the vector number "N".

- In the 2nd INTA cycle, 8259 sends the vector number (Type Number) "N", to the microprocessor, through the multiplexed address data bus.

- The microprocessor then multiplies the number by 4 and goes to the corresponding location in

- From there it obtains the values of Segment Address and Offset Address for the ISR of the corresponding interrupt, and hence executes the ISR.

- LOCK signal is held low between the two INTA cycles, so that the bus is not released in between this process.

## Addressing Modes of 8086

8086 provides different addressing modes for Data, Program and Stack Memory.

## **ADDRESSING MODES FOR DATA MEMORY** {IMP}

## I IMMEDIATE ADDRESSING MODE

In this mode the **operand** is specified in the **instruction** itself. Instructions are **longer** but the **operands** are **easily identified**.

**Eg:** MOV CL, 12H ; Moves 12 immediately into CL register MOV BX, 1234H ; Moves 1234 immediately into BX register

## IIREGISTER ADDRESSING MODE

In this mode **operands** are specified using **registers**.

Instructions are **shorter** but **operands cant** be **identified** by looking at the instruction.

**Eg:** MOV CL, DL ; Moves data of DL register into CL register MOV AX, BX ; Moves data of BX register into AX register

## III DIRECT ADDRESSING MODE

In this mode **address** of the operand is directly specified **in the instruction**. Here **only** the **offset address is specified**, the segment being indicated by the instruction.

```

Eg: MOV CL, [4321H] ; Moves data from location 4321H in the data ; segment into CL ; The physical address is calculated as ; DS * 10_H + 4321 ; Assume DS = 5000H ; \therefore P A= 50000 + 4321 = 54321H ; \therefore CL \leftarrow [54321H]

Eg: MOV CX, [4320H] ; Moves data from location 4320H and 4321H ; in the data segment into CL and CH resp.

```

## IV INDIRECT ADDRESSING MODES

## REGISTER INDIRECT ADDRESSING MODE

In this mode the  $\mu P$  uses any of the 2 **base registers** BP, BX or any of the two index registers SI, DI to provide the offset **address** for the data byte.

```

The segment is indicated by the Base Registers: BX -- Data Segment, BP --- Stack Segment

```

```

Eg:MOV CL, [BX]; Moves a byte from the address pointed by BX in Data<br/>; Segment into CL.<br/>; Physical Address calculated as DS * 10_H + BXEg:MOV [BP], CL; Moves a byte from CL into the location pointed by BP in<br/>; Stack Segment.<br/>; Physical Address calculated as SS * 10_H + BP

```

## REGISTER RELATIVE ADDRESSING MODE

In this mode the operand address is calculated using one of the **base registers** and a **8-bit** or a **16-bit displacement.**

```

Eg:MOV CL, [BX+4] ; Moves a byte from the address pointed by BX+4 in ; Data Seg to CL. ; Physical Address: DS*10_H + BX + 4H

Eg: MOV 12H [BP], CL ; Moves a byte from CL to location pointed by BP+12H in ; the Stack Seg. ; Physical Address: SS*10_H + BP + 12H

```

# BASE INDEXED ADDRESSING MODE

Here, operand address is calculated as Base register plus an Index register.

```

Eg: MOV CL, [BX+SI] ; Moves a byte from the address pointed by BX+SI; in Data Segment to CL.; Physical Address: DS * 10_H + BX + SI

Eg: MOV [BP+DI], CL ; Moves a byte from CL into the address pointed by ; BP+DI in Stack Segment.; Physical Address: SS * 10_H + BP + DI

```

## BASE RELATIVE PLUS INDEX ADDRESSING MODE

In this mode the address of the operand is calculated as Base register plus Index register plus 8-bit or 16-bit displacement.

Eq: MOV CL, [BX+DI+20] ; Moves a byte from the address pointed by ; BX+SI+20H in Data Segment to CL. ; Physical Address: DS \* 10<sub>H</sub> + BX + SI+ 20H Eq: MOV [BP+SI+2000], CL ; Moves a byte from CL into the location pointed by

; BP+SI+2000H in Stack Segment.

; Physical Address: SS \* 10H + BP+SI+2000H

## V IMPLIED ADDRESSING MODE

In this addressing mode the operands are implied and are hence not specified in the instruction. #Please refer Bharat Sir's Lecture Notes for this ...

Eq: STC ; Sets the Carry Flag.

Eg: CLD ; Clears the Direction Flag.

#### Important points for understanding addressing modes...

- 1) Anything given in square brackets will be an Offset Address also called Effective Address.

- MOV instruction by default operates on the Data Segment; unless specified otherwise.

- BX and BP are called Base Registers. BX holds Offset Address for Data Segment. BP holds Offset Address for Stack Segment.

- 4) SI and DI are called Index Registers

- 5) The Segment to be operated is decided by the Base Register and NOT by the Index Register.

## ADDRESSING MODES FOR PROGRAM MEMORY

(optional --- to be written only if asked)

This addressing mode is required for instructions that **cause a branch** in the program. If the Branch is **within the same segment**, it is called as an **Intra-Segment Branch** or a **Near** Branch. If the Branch is **in a different segment**, it is called as an **Inter-Segment Branch** or a **Far** Branch.

## INTRA SEGMENT DIRECT ADDRESSING MODE

Address is specified directly in the instruction as an 8-bit (or 16-bit) displacement. The effective address is thus calculated by adding the displacement to current value of IP. As it is intra-segment, ONLY IP changes, CS does not change.

If the displacement is 8-bit it is called as a Short Branch.

This addressing mode is also called as **relative addressing mode**.

| Ēg: | Code              | SEGMENT                                                       |

|-----|-------------------|---------------------------------------------------------------|

|     | Prev:             |                                                               |

|     | Current: <b>J</b> | <b>AP Prev</b> : $IP \leftarrow Offset \ address \ of "Prev"$ |

|     | Code              | ENDS                                                          |

|     |                   | Or                                                            |

|     | Code              | SEGMENT                                                       |

|     | Current: 3        | MP Next                                                       |

|     | Next:             |                                                               |

|     | Codo              | ENDS                                                          |

## INTER SEGMENT DIRECT ADDRESSING MODE

The new Branch location is **specified directly** in the instruction Both **CS and IP get new values**, as this is an inter-segment branch. Eq:

| Code_1      | SEGMENT    |                                                                           |

|-------------|------------|---------------------------------------------------------------------------|

| Current: JN | MP NextSeg | ; CS ← Segment address of "NextSeg"<br>, IP ← Offset address of "NextSeg" |

| Code_1      | ENDS       | )                                                                         |

| Code_2      | SEGMENT    |                                                                           |

| NextSeg:    |            |                                                                           |

| Code_2      | ENDS       |                                                                           |

# INTRA SEGMENT INDIRECT ADDRESSING MODE

Address is specified indirectly through a register or a memory location (in DS only). The value in the IP is replaced with the new value. As it is intra-segment, ONLY IP changes, CS does not change.

JMP WORD PTR [BX] ;  $IP \leftarrow \{DS:[BX], DS:[BX+1]\}$ Eq:

# INTER SEGMENT INDIRECT ADDRESSING MODE

The new Branch location is specified indirectly through a register or a memory location (in DS only). #Please refer Bharat Sir's Lecture Notes for this ...

Both CS and IP get new values, as this is an inter-segment branch.

; IP ← {DS:[BX], DS:[BX+1]}, Eq: JMP DWORD PTR [BX] ; CS ← {DS:[BX+2], DS:[BX+3]}

# ADDRESSING MODES FOR STACK MEMORY (optional, to be written only if asked)

## REGISTER ADDRESSING MODE

Here the **operands** are specified **in registers** (ONLY 16-bit registers).

EG: PUSH BX; Transfers BH at location pointed by SP-1 and BL at location ; pointed by SP-2 in the Stack segment. Also SP  $\leftarrow$  SP - 2.

# REGISTER INDIRECT ADDRESSING MODE

Here the address of the operand is specified in the registers.

; Transfers a word from location pointed by BX and BX+1 in Eg: PUSH [BX] ; data segment to SP-1 and SP-2 in Stack Segment.

## 1) Flag Addressing Mode

Here the contents of Flag register are transferred to and from the Stack.

; Transfers higher byte of Flag register to SP-1 Eg: PUSHF ; and lower byte to SP-2 in the Stack Segment.

## 2) Segment Register Addressing Mode

Here the segment registers (except CS) are transferred to and from the Stack.

Eg: PUSH DS; Transfers higher byte of DS register to location ; SP - 1 and lower byte to SP-2 in the Stack Segment.

# 8086 SOFTWARE MODEL

# **8086 Instruction Set**

## CLASSIFICATION OF INSTRUCTION SET OF 8086

1) DATA TRANSFER INSTRUCTIONS

E.g.:: MOV, PUSH, POP

2) ARITHMETIC INSTRUCTIONS

E.g.:: ADD, SUB, MUL

3) LOGIC INSTRUCTIONS (BIT MANIPULATION INSTRUCTIONS)

E.g.:: AND, OR, XOR

4) SHIFT INSTRUCTIONS & ROTATE INSTRUCTIONS

E.g.:: ROL, RCL, ROR, SHL

5) PROGRAM EXECUTION AND TRANSFER INSTRUCTIONS (BRANCH INSTRUCTIONS)

E.g.:: JMP, CALL, JC

6) ITERATION CONTROL INSTRUCTIONS (LOOP INSTRUCTIONS)

E.g.:: LOOP, LOOPZ, LOOPNE

7) PROCESSOR CONTROL INSTRUCTIONS (INSTRUCTIONS OPERATING ON FLAGS)

E.g.:: STC, CLC, CMC

8) EXTERNAL HARDWARE SYNCHRONIZATION INSTRUCTIONS

E.g.:: LOCK, ESC, WAIT

9) INTERRUPT CONTROL INSTRUCTIONS

E.g.:: INT n, IRET, INTO (Interrupt on overflow)

10) STRING INSTRUCTIONS

E.g.:: MOVSB, LODSB, STOSB

## **Data Transfer Instructions**

#### 1) MOV Destination, Source

Moves a byte/word from the source to the destination specified in the instruction.

Source: Register, Memory Location, Immediate Number

Destination: Register, Memory Location

Both, source and destination cannot be memory locations.

Eg: MOV CX, 0037H ; CX ← 0037H MOV BL, [4000H] ; BL ← DS:[4000H]

MOV AX, BX;  $AX \leftarrow BX$ MOV DL, [BX];  $DL \leftarrow DS:[BX]$ MOV DS, BX;  $DS \leftarrow BX$

#### 2) PUSH Source

Push the source (word) into the stack and decrement the stack pointer by two.

The source MUST be a WORD (16 bits).

Source: Register, Memory Location

Eg: **PUSH CX** ;  $SS:[SP-1] \leftarrow CH$ ,  $SS:[SP-2] \leftarrow CL$

; SP + SP - 2

**PUSH DS** ; *SS*:[*SP*-1, *SP*-2] ← *DS*

; SP SP - 2

#### 3) POP Destination

**POP** a **word from** the **stack** into the given destination and increment the Stack Pointer by 2. The destination MUST be a **WORD** (16 bits).

Destination: Register [EXCEPT CS], Memory Location

Eg: **POP CX** ;  $CH \leftarrow SS:[SP], CL \leftarrow SS:[SP+1]$

; SP + SP + 2

**POP DS** ;  $DS \leftarrow SS:[SP, SP+1]$

; SP SP + 2

**Please Note**: MOV, PUSH, POP are the ONLY instructions that use the Segment Registers as operands {except CS}.

#### 4) PUSHF

Push value of Flag Register into stack and decrement the stack pointer by 2.

Eg: **PUSHF** ;  $SS:[SP-1] \leftarrow Flag_H$ ,  $SS:[SP-2] \leftarrow Flag_L$ ,  $SP \leftarrow SP - 2$

#### 5) POPF

POP a word from the stack into the Flag register.

Eg: **POPF** ;  $Flag_L \leftarrow SS:[SP]$ ,  $Flag_H \leftarrow SS:[SP+1]$ ,  $SP \leftarrow SP + 2$

#### 6) XCHG Destination, Source

Exchanges a byte/word between the source and the destination specified in the instruction.

Source: Register, Memory Location Destination: Register, Memory Location

Even here, both operands cannot be memory locations.

Eg: XCHG CX, BX ;  $CX \leftarrow \rightarrow BX$  XCHG BL, CH ;  $BL \leftarrow \rightarrow CH$

#### 7) XLATB / XLAT (very important)

Move into AL, the contents of the memory location in Data Segment, whose effective address is formed by the sum of BX and AL.

Eg: **XLAT** ;  $AL \leftarrow DS:[BX + AL]$  ; i.e. if DS = 1000H; BX = 0200H; AL = 03H ;  $\therefore$  10000 ... DS × 16 ; + 0200 ... BX ; + 03 ... AL ; = 10203  $\therefore$  AL  $\leftarrow$  [10203H]

Note: the difference between XLAT and XLATB

## In XLATB there is no operand in the instruction.

E.g.:: XLATB

It works in an implied mode and does exactly what is shown above.

## In XLAT, we can specify the name of the look up table in the instruction

E.g.:: XLAT SevenSeg

This will do the translation form the look up table called SevenSeg.

In any case, the base address of the look up table must be given by BX.

#### 8) LAHF

Loads AH with lower byte of the Flag Register.

#### 9) SAHF

Stores the contents of AH into the lower byte of the Flag Register.

#### 10)LEA register, source

Loads Effective Address (offset address) of the source into the given register.

Eg: **LEA BX, Total** ; BX ← offset address of Total in Data Segment.

## 11)LDS destination register, source

Loads the destination register and DS register with offset address and segment address specified by the source.

```

Eg: LDS BX, Total ; BX \leftarrow \{DS:[Total], DS:[Total + 1]\}, ; DS \leftarrow \{DS:[Total + 2], DS:[Total + 3]\}

```

## 12)LES destination register, source

Loads the **destination register and ES** register with the **offset address and** the **segment address** indirectly specified by the **source**.

```

Eg: LES BX, Total ; BX \leftarrow \{DS:[Total], DS:[Total + 1]\}, ; ES \leftarrow \{DS:[Total + 2], DS:[Total + 3]\}

```

## **I/O ADDRESSING MODES OF 8086** (5m - Important Question)

I/O addresses in 8086 can be either 8-bit or 16-bit

## Direct Addressing Mode:

If we use 8-bit I/O address we get a range of 00H... FFH.

This gives a total of **256 I/O ports**.

Here we use Direct addressing Mode, that is, the I/O address is specified in the instruction.

E.g.:: IN AL, 80H ; AL gets data from I/O port address 80H.

This is also called **Fixed Port Addressing**.

## Indirect Addressing Mode:

If we use 16-bit I/O address we get a range of 0000H... FFFFH.

This gives a total of 65536 I/O ports.

Here we use Indirect addressing Mode, that is, the I/O address is specified by DX register.

E.g.:: MOV DX, 2000H IN AL, DX

; AL gets data from I/O port address 2000H given by DX.

This is also called Variable Port Addressing.

#### 13)IN destination register, source port

Loads the destination register with the contents of the I/O port specified by the source.

Source: It is an I/O port address.

If the address is 8-bit it will be given in the instruction by **Direct addressing mode.**If it is a 16 bit address it will be given by DX register using **Indirect addressing mode.**

Destination: It has to be some form of "A" register, in which we will get data from the I/O device. If we are getting 8-bit data, it will be AL or AH register.

If we are getting 16-bit data, it will be AX register.

Eg: IN AL, 80H

IN AX, 80H

; AL gets 8-bit data from I/O port address 80H

; AX gets 16-bit data from I/O port address 80H

; AL gets 8-bit data from I/O port address given by DX.

IN AX, DX

; AX gets 16-bit data from I/O port address given by DX.

#### 14)OUT destination port, source register

Loads the destination I/O port with the contents of the source register.

Eg: OUT 80H, AL ; I/O port 80H gets 8-bit data from AL ; I/O port 80H gets 16-bit data from AX

OUT DX, AL ; I/O port whose address is given by DX gets 8-bit data from AL OUT DX, AX ; I/O port whose address is given by DX gets 16-bit data from AX

## **Segment Overriding**

In every instruction, a particular segment register is accessed for the base address.

Eg: MOV CL, [5000H] ; CL← DS:[5000H] as Data Seg is accessed by default

However, we can also override the segment as follows:

Eg: MOV CL, CS:[5000H] ; Here CL ← CS:[5000H], this is Segment Overriding.

By default, the address 5000H would have been an offset for the data segment, BUT here we **override** it with the Code segment as shown above.

## Another example:

MOV BL, [BP] ; BL ← SS:[BP] ... Normal MOV BL, DS:[BP] ; BL ← DS:[BP] ... Overriding

# **Arithmetic Instructions**

Adds the source to the destination and stores the result back in the destination. 1) ADD/ADC destination, source

Source: Register, Memory Location, Immediate Number

Destination: Register Both, source and destination have to be of the same size.

ADC also adds the carry into the result.

; AL ← AL + 25H Eg: ADD AL, 25H ; BL ← BL + CL ADD BL, CL ; BX ← BX + CX ADD BX, CX

; BX ← BX + CX + Carry Flag ADC BX, CX

2) SUB/SBB destination, source

It is similar to ADD/ADC except that it does subtraction.

3) INC destination

Adds "1" to the specified destination.

Destination: Register, Memory Location

Note: Carry Flag is NOT affected.

;  $AX \leftarrow AX + 1$ Eg: INC AX ; BL ← BL + 1 INC BL

; Increment the **byte** pointed by BX in the Data Segment INC BYTE PTR [BX]

; i.e. DS:[BX] ← DS;[BX] + 1

; Increment word pointed by BX in the Data Segment INC WORD PTR [BX]

; {DS:[BX], DS:[BX+1]} ← {DS:[BX], DS:[BX+1]}+1

4) DEC destination

It is similar to INC. Here also Carry Flag is NOT affected.

5) MUL source(unsigned 8/16-bit register)

If the source is 8-bit, it is multiplied with AL and the result is stored in AX (AH-higher byte, AL-

If the source is 16-bit, it is multiplied with AX and the result is stored in DX-AX (DX-higher byte, AX-lower byte)

Source: Register, Memory Location MUL affects AF, PF, SF and ZF.

; AX ← AL × BL Eq: MUL BL ; DX-AX ← AX × BX **MUL BX** ; AX ← AL × DS:[BX] MUL BYTE PTR [BX]

6) IMUL source(signed 8/16-bit register)

Same as MUL except that the source is a SIGNED number.

7) DIV source(unsigned 8/16-bit register - divisor)

This instruction is used for **UNSIGNED** division.

Divides a WORD by a BYTE, OR a DOUBLE WORD by a WORD.

If the divisor is 8-bit then the dividend is in AX register.

After division, the quotient is in AL and the Remainder in AH.

If the divisor is 16-bit then the dividend is in DX-AX registers.

After division, the quotient is in AX and the Remainder in DX.

Source: Register, Memory Location © For doubts contact Bharat Sir on 98204 08217 ALL flags are undefined after DIV instruction.

Eg: **DIV BL** ; AX ÷ BL :- AL ← Quotient; AH ← Remainder

**DIV BX** ;  $\{DX,AX\} \div BX :- AX \leftarrow Quotient; DX \leftarrow Remainder$

**Please Note:** If the divisor is 0 or the result is too large to fit in AL (or AX for 16-bit divisor), them 8086 does a Type 0 interrupt (Divide Error).

8) IDIV source(signed 8/16-bit register – divisor)

Same as DIV except that it is used for **SIGNED** division.

9) NEG destination

This instruction forms the 2's complement of the destination, and stores it back in the destination.

Destination: Register, Memory Location

ALL condition flags are updated.

Eg: **Assume** AL= 0011 0101 = 35 H then

NEG AL ;AL ← 1100 1011 = CBH. i.e. AL ← 2's Complement (AL)

10)CMP destination, source

This instruction compares the source with the destination.

The source and the destination must be of the same size.

Comparison is done by internally SUBTRACTING the SOURCE form DESTINATION.

The result of this subtraction is NOT stored anywhere, instead the Flag bits are affected.

Source: Register, Memory Location, Immediate Value

Destination: Register, Memory Location

ALL condition flags are updated.

Eg: CMP BL, 55H ; BL compared with 55H i.e. BL - 55H.

CMP CX, BX; CX compared with BX i.e. CX - BX.

11)CBW [Convert signed BYTE to signed WORD]

This instruction copies sign of the byte in AL into all the bits of AH.

AH is then called sign extension of AL.

No Flags affected.

Eg: Assume

AX = XXXX XXXX 1001 0001

Then **CBW** gives

AX = 1111 1111 1001 0001

12)CWD [Convert signed WORD to signed DOUBLE WORD]

This instruction copies sign of the WORD in AX into all the bits of DX.

DX is then called sign extension of AX.

No Flags affected.

Eg: Assume

AX = 1000 0000 1001 0001

DX = XXXX XXXX XXXX XXXX

Then **CWD** gives

AX = 1000 0000 1001 0001

DX = 1111 1111 1111 1111

Note: Both CBW and CWD are used for Signed Numbers.

## **Decimal Adjust Instructions**

#### 13)DAA [Decimal Adjust for Addition]

It makes the result in packed BCD form after BCD addition is performed.

It works **ONLY** on **AL** register.

All Flags are updated; OF becomes undefined after this instruction.

#### For AL register ONLY

If  $D_3 - D_0 > 9$  OR Auxiliary Carry Flag is set => ADD 06H to AL.

If  $D_7 - D_4 > 9$  OR Carry Flag is set => ADD 60H to AL.

## Assume AL = 14H

CL = 28H

Then ADD AL, CL gives

AL = 3CH

Now DAA gives

AL = 42 (06 is added to AL as C > 9)

If you notice,  $(14)_{10} + (28)_{10} = (42)_{10}$

#### 14)DAS [Decimal Adjust for Subtraction]

It makes the result in packed BCD form after BCD subtraction is performed.

It works ONLY on AL register.

All Flags are updated; OF becomes undefined after this instruction.

#### For AL register ONLY

If  $D_3 - D_0 > 9$  OR Auxiliary Carry Flag is set => Subtract 06H from AL.

If  $D_7 - D_4 > 9$  OR Carry Flag is set => Subtract 60H from AL.

#### Assume AL = 86H

CL = 57H

Then SUB AL, CL gives

AL = 2FH

Now **DAS** gives

AL = 29 (06 is subtracted from AL as F > 9)

If you notice,  $(86)_{10}$  -  $(57)_{10}$  =  $(29)_{10}$

## **ASCII Adjust Instructions** (for the AX register ONLY)

#### 15) AAA [ASCII Adjust for Addition]

It makes the result in unpacked BCD form.

In ASCII Codes, 0 ... 9 are represented as 30 ... 39.

When we add ASCII Codes, we need to mask the higher byte (Eg: 3 of 39).

This can be avoided if we use AAA instruction after the addition is performed.

AAA updates the AF and the CF; But OF, PF, SF, ZF are undefined after the instruction.

<u>Eg: Assume</u>

AL = 0011 0100 ... ASCII 4.

CL = 0011 1000 ... ASCII 8.

Then ADD AL, CL gives

AL = 01101100

i.e. AL = 6CH ... it is the Incorrect temporary Result

#### Now AAA gives

AL = 0000 0010 ... Unpacked BCD for 2.

Carry =  $1 \dots$  this indicates that the answer is 12.

#### 16)AAS [ASCII Adjust for Subtraction]

It makes the result in unpacked BCD form.

In ASCII Codes, 0 ... 9 are represented as 30 ... 39.

When we subtract ASCII Codes, we need to mask the higher byte (Eg: 3 of 39).

This can be avoided if we use AAS instruction after the subtraction is performed.

AAS updates the AF and the CF; But OF, PF, SF, ZF are undefined after the instruction.

Eg: Assume

AL = 0011 1001 ... ASCII 9.

CL = 0011 0101 ... ASCII 5.

Then SUB AL, CL gives

AL = 0000 0100

i.e. AL = 04H

Now AAS gives

$AL = 0000 \ 0100 \dots Unpacked BCD for 4.$

Carry = 0 ... this indicates that the answer is 04.

#### 17)AAM [BCD Adjust After Multiplication]

Before we multiply two ASCII digits, we mask their upper 4 bits.

Thus we have two unpacked BCD operands.

After the two unpacked BCD operands are multiplied, the AAM instruction converts this result into unpacked BCD form in the AX register.

AAS updates PF, SF ZF; But OF, AF, CF are undefined after the instruction.

#### Eg: Assume

AL = 0000 1001 ... unpacked BCD 9.

CL = 0000 0101 ... unpacked BCD 5.

Then MUL CL gives

$AX = 0000\ 0000\ 0010\ 1101 = 002DH.$

Now AAM gives

$AX = 0000\ 0100\ 0000\ 0101 = 0405H.$

This is 45 in the unpacked BCD form.

#### 18)AAD [Binary Adjust before Division]

This instruction converts the unpacked BCD digits in AH and Al into a Packed BCD in AL.

AAD updates PF, SF ZF; But OF, AF, CF are undefined after the instruction.

#### Eg: Assume

CL = 07H.

AH = 04.

AL = 03.

$\therefore$  AX = 0403H ... unpacked BCD for (43)<sub>10</sub>

Then AAD gives

$AX = 002BH ... i.e. (43)_{10}$

Now DIV CL gives (divide AX by unpacked BCD in CL)

AL = Quotient = 06 ... unpacked BCD

AH = Remainder = 01 ... unpacked BCD

# LOGICAL INSTRUCTIONS [BIT MANIPULATION INSTRUCTIONS]

## 1) NOT destination

This instruction forms the 1's complement of the destination, and stores it back in the destination. Destination: Register, Memory Location. No Flags affected.

Eg: **Assume** AL= 0011 0101

**NOT AL** ; AL ← 1100 1010 ... i.e. AL = 1's Complement (AL)

## 2) AND destination, source

This instruction logically ANDs the source with the destination and stores the result in the destination. Source and destination have to be of the same size.

Source: Register, Memory Location, Immediate Value

Destination: Register, Memory Location

PF, SF, ZF affected; CF, OF ← 0; AF becomes undefined.

Eg: AND BL, CL ; BL BL AND CL

## 3) OR destination, source

This instruction logically Ors the source with the destination and stores the result in the destination. Source and destination have to be of the same size.

Source: Register, Memory Location, Immediate Value

Destination: Register, Memory Location

PF, SF, ZF affected; CF, OF ← 0; AF becomes undefined.

Eg: OR BL, CL ; BL ← BL OR CL

## 4) XOR destination, source

This instruction logically X-Ors the source with the destination and stores the result in the destination. Source and destination have to be of the same size.

Source: Register, Memory Location, Immediate Value

Destination: Register, Memory Location

PF, SF, ZF affected; CF, OF ← 0; AF becomes undefined.

Eg: XOR BL, CL ; BL ← BL XOR CL

#### 5) TEST destination, source

This instruction logically ANDs the source with the destination BUT the RESULT is NOT STORED ANYWHERE. ONLY the FLAG bits are AFFECTED.

Source: Register, Memory Location, Immediate Value

Destination: Register, Memory Location

PF, SF, ZF affected; CF, OF ← 0; AF becomes undefined.

Eg: **TEST BL, CL** ; BL AND CL; result not stored; Flags affected.

Note: Don't forget this instruction because it will be used later in multiprocessor systems!

# **SHIFT INSTRUCTIONS**

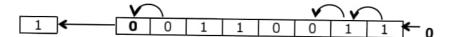

#### 1) SAL/SHL destination, count

LEFT-Shifts the bits of destination.

MSB shifted into the CARRY.

LSB gets a 0.

Bits are shifted 'count' number of times.

If count = 1, it is directly specified in the instruction.

If count > 1, it has to be given using CL Register.

Destination: Register, Memory Location. #Please refer Bharat Sir's Lecture Notes for this ...

Eg: **SAL BL, 1** ; Left-Shift BL bits, once.

#### Assume:

Before Operation: BL = 0011 0011 and CF = 1

Carry Destination

After Operation: BL = 0110 0110 and CF = 0

| _ 0 _ ← | O | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|

More examples:

MOV CL, 05H

; Load number of shifts in CL register.

SAL BL, CL

; Left-Shift BL bits CL (5) number of times.

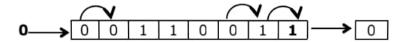

#### 2) SHR destination, count

RIGHT-Shifts the bits of destination.

MSB gets a 0 (∴ Sign is lost).

LSB shifted into the CARRY.

Bits are shifted 'count' number of times.

If count is 1, it is directly specified in the instruction.

If count > 1, it has to be given using CL register.

Eg: **SHR BL, 1**

; Right-Shift BL bits, once.

#### Assume:

Before Operation: BL = 0011 0011 and CF = 0

#### Destination

Carry

After Operation: BL = 00011 1001 and CF = 1

| 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | <b>─</b> | 1 |

|---|---|---|---|---|---|---|---|----------|---|

|---|---|---|---|---|---|---|---|----------|---|

#### 3) SAR destination, count

**RIGHT-Shifts** the bits of destination.

**MSB** placed **in MSB itself** (: Sign is preserved).

LSB shifted into the CARRY.

Bits are shifted 'count' number of times.

If count is 1, it is directly specified in the instruction.

If count > 1 it has to be given using CL register. © For doubts contact Bharat Sir on 98204 08217 Destination: Register, Memory Location

Eg: **SAR BL, 1**

; Right-Shift BL bits, once.

#### Assume:

Before Operation: BL = 0011 0011 and CF = 0

#### Destination

Carry

After Operation: BL = 0001 1001 and CF = 1

# **ROTATE INSTRUCTIONS**

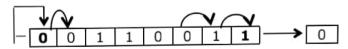

#### 1) ROL destination, count

LEFT-Shifts the bits of destination.

MSB shifted into the CARRY.

MSB also goes to LSB.

Bits are shifted 'count' number of times.

If count = 1, it is directly specified in the instruction.

If count > 1, it has to be loaded in the CL register, and CL gives the count in the instruction.

Destination: Register, Memory Location

Eg: ROL BL, 1 ; Left-Shift BL bits once.

#### Carry

#### Destination

More examples:

MOV CL, 05H ROL BL, CL

; Load number of shifts in CL register.

; Left-Shift BL bits CL (5) number of times.

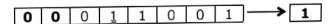

#### 2) ROR destination, count

RIGHT-Shifts the bits of destination.

LSB shifted into the CARRY.

LSB also goes to MSB.

Bits are shifted 'count' number of times.

If count = 1, it is directly specified in the instruction.

If count > 1, it has to be loaded in the CL register, and CL gives the count in the instruction.

Eg:

ROR BL, 1

; Right-Shift BL bits once.

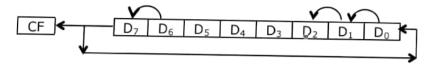

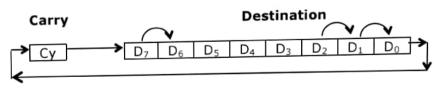

# 3) RCL destination, count

**LEFT-Shifts** the bits of destination.

MSB shifted into the Carry Flag (CF).

CF goes to LSB.

Bits are shifted 'count' number of times.

If count = 1, it is directly specified in the instruction.

If count > 1, it has to be loaded in the CL register, and CL is specified as the count in the instruction.

Destination: Register, Memory Location

; Left-Shift BL bits once. Eg: RCL BL, 1

#### **Destination** Carry $D_4$ D٦ $D_5$ CF

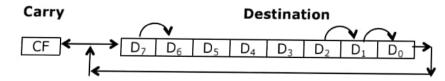

### 4) RCR destination, count

RIGHT-Shifts the bits of destination.

LSB shifted into the CF.

CF goes to MSB.

Bits are shifted 'count' number of times.

If count = 1, it is directly specified in the instruction.

If count > 1, it has to be loaded in the CL register, and CL is specified as the count in the instruction.

Destination: Register, Memory Location

Eg:

; Right-Shift BL bits once. RCR BL, 1

More examples:

; Load number of shifts in CL register. MOV CL, 05H ; Right-Shift BL bits CL (5) number of times. RCR BL, CL

# PROGRAM EXECUTION AND TRANSFER INSTRUCTIONS

These instructions cause a branch in the program sequence.

There are 2 main types of branching:

- Near branch

- Far Branch ii.

#### **Near Branch**

This is an Intra-Segment Branch i.e. the branch is to a new location within the current segment

Thus, only the value of IP needs to be changed.

If the Near Branch is in the range of -128 to 127, then it is called as a Short Branch.

#### ii. Far Branch

This is an Inter-Segment Branch i.e. the branch is to a new location in a different segment. Thus, the values of CS and IP need to be changed.

**JMP** (Unconditional Jump)

### INTRA-Segment (NEAR) JUMP

The Jump address is specified in two ways:

### 1) INTRA-Segment Direct Jump

The new Branch location is specified directly in the instruction

The new address is calculated by adding the 8 or16-bit displacement to the IP.

The CS does not change.

A +ve displacement means that the Jump is ahead (forward) in the program.

A -ve displacement means that the Jump is behind (backward) in the program.

It is also called as Relative Jump.

; IP ← offset address of "Prev". Eq: JMP Prev : IP ← offset address of "Next". JMP Next

#### 2) INTRA-Segment Indirect Jump

The New Branch address is specified indirectly through a register or a memory location.

The value in the IP is replaced with the new value.

The CS does not change.

; IP ← {DS:[BX], DS: [BX+1]} Eq: JMP WORD PTR [BX]

#### **INTER-Segment (FAR) JUMP**

The Jump address is specified in two ways:

## 3) INTER-Segment Direct Jump

The new Branch location is specified directly in the instruction

Both CS and IP get new values, as this is an inter-segment jump.

Eg: Assume NextSeg is a label pointing to an instruction in a different segment.

; CS and IP get the value from the label NextSeg. JMP NextSeg

## 4) INTER-Segment Indirect Jump

The new Branch location is specified indirectly through a register or a memory location.

Both CS and IP get new values, as this is an inter-segment jump. ; IP ← {DS:[BX], DS: [BX+1]}, Eq:JMP DWORD PTR [BX]

; CS ← {DS:[BX+2], DS:[BX+3]}

# **JCondition** (Conditional Jump)

This is a conditional branch instruction.

If condition is TRUE, then it is similar to an INTRA-Segment Direct Jump.

If condition is FALSE, then branch does not take place and the next sequential instruction is executed. The destination must be in the range of -128 to 127 from the address of the instruction (i.e. ONLY SHORT Jump).

**JNC Next** Ea:

; Jump to Next If Carry Flag is not set (CF = 0).

The various conditional jump instructions are as follows:

| Mnemonic  | Description              | Jump Condition           |  |  |

|-----------|--------------------------|--------------------------|--|--|

| Timemonie | Common Operations        |                          |  |  |

| JC        | Carry                    | CF = 1                   |  |  |

| JNC       | Not Carry                | CF = 0                   |  |  |

| JE/JZ     | Equal or Zero            | <u>z</u> F = 1           |  |  |

| JNE/JNZ   | Not Equal or Not Zero    | ZF = 0                   |  |  |

| JP/JPE    | Parity or Parity Even    | PF = 1                   |  |  |

| JNP/JPO   | Not Parity or Parity Odd | PF = 0                   |  |  |

|           | Signed Operations        |                          |  |  |

| 30        | Overflow                 | OF = 1                   |  |  |

| JNO       | Not Overflow             | OF = 0                   |  |  |

| JS        | Sign                     | SF = 1                   |  |  |

| JNS       | Not Sign                 | SF = 0                   |  |  |

| JL/JNGE   | Less                     | (SF Ex-Or OF) = 1        |  |  |

| JGE/JNL   | Greater or Equal         | (SF Ex-Or OF) = 0        |  |  |

| JLE/JNG   | Less or Equal            | ((SF Ex-Or OF) + ZF) = 1 |  |  |

| JG/JNLE   | Greater                  | ((SF Ex-Or OF) + ZF) = 0 |  |  |

|           | Unsigned Operations      |                          |  |  |

| JB/JNAE   | Below                    | CF = 1                   |  |  |

| JAE/JNB   | Above or Equal           | CF = 0                   |  |  |

| JBE/JNA   | Below or Equal           | (CF Ex-Or ZF) = 1        |  |  |

| JA/JNBE   | Above                    | (CF Ex-Or ZF) = 0        |  |  |

# **CALL** (Unconditional CALL)

CALL is an instruction that transfers the program control to a sub-routine, with the intention of coming back to the main program.

Thus, in CALL 8086 saves the address of the next instruction into the stack before branching to the sub-routine.

At the end of the subroutine, control transfers back to the main program using the return address from the stack.

There are two types of CALL: Near CALL and Far CALL.

#### INTRA-Segment (NEAR) CALL

The new subroutine called must be in the same segment (hence intra-segment).

The CALL address can be specified directly in the instruction OR indirectly through Registers or Memory Locations.

The following sequence is executed for a NEAR CALL:

- 8086 will PUSH Current IP into the Stack.

- ii. Decrement SP by 2.

- iii. New value loaded into IP.

```

iv. Control transferred to a subroutine within the same segment.

; {SS:[SP-1], SS:[SP-2]} ← IP, SP ← SP - 2,

Eg: CALL subAdd

; IP 	New Offset Address of subAdd.

```

## INTER-Segment (FAR) CALL

The new subroutine called is in another segment (hence inter-segment).

Here CS and IP both get new values.

The CALL address can be specified directly OR through Registers or Memory Locations. The following sequence is executed for a Far CALL:

- PUSH CS into the Stack.

- ii. Decrement SP by 2.

- iii. PUSH IP into the Stack.

- iv. Decrement SP by 2.

- v. Load CS with new segment address.

- vi. Load IP with new offset address.

- vii. Control transferred to a subroutine in the new segment.

```

; {SS:[SP-1], SS:[SP-2]} ← CS, SP ← SP - 2,

CALL subAdd

Eg:

; {SS:[SP-1], SS:[SP-2]} ← CS, SP ← SP - 2,

; CS ← New Segment Address of subAdd,

; IP ← New Offset Address of subAdd.

```

There is NO PROVISION for Conditional CALL.

# **RET --- Return instruction**

RET instruction causes the control to return to the main program from the subroutine.

; IP  $\leftarrow$  SS:[SP], SS:[SP+1]

#### Intrasegment-RET

Eg: RET

```

; SP \leftarrow SP + 2

; IP \leftarrow SS:[SP], SS:[SP+1]

RET n

; SP \leftarrow SP + 2 + n

Intersegment-RET

; IP \leftarrow SS:[SP], SS:[SP+1]

Eg: RET

; CS ← SS:[SP+2], SS:[SP+3]

; SP ← SP + 4

RET n

; IP \leftarrow SS:[SP], SS:[SP+1]

; CS ← SS:[SP+2], SS:[SP+3]

; SP \leftarrow SP + 4 + n

```

Please Note: The programmer writes the intra-seg and Inter-seg RET instructions in the same way. It is the assembler, which distinguishes between the two and puts the right opcode. #Please refer Bharat Sir's Lecture Notes for this

|   | JMP Instruction                                                                      | CALL INSTRUCTION                                                                                        |

|---|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 1 | JMP instruction is used to <b>jump to a new location</b> in the program and continue | Call instruction is used to invoke a subroutine, execute it and then return to the main program.        |

| 2 | A jump simply puts the branch address into IP.                                       | A call <b>first stores the return address into the stack</b> and then loads the branch address into IP. |

| 3 | In 8086 Jumps can be either unconditional or conditional.                            | In 8086, Calls are only <b>unconditional</b> .                                                          |

| 4 | Does not use the stack                                                               | Uses the stack                                                                                          |

| 5 | Does <b>not need a RET</b> instruction.                                              | <b>Needs a RET</b> instruction to return back to main program.                                          |

|   | PROCEDURE (FUNCTION)                                                                                                                                                           | Macro                                                                                                                                                                                     |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | A procedure (Subroutine/ Function) is a set of instruction needed repeatedly by the program. It is stored as a subroutine and invoked from several places by the main program. | A Macro is similar to a procedure but is not invoked by the main program. Instead, the Macro code is pasted into the main program wherever the macro name is written in the main program. |

| 2 | A subroutine is <b>invoked by a CALL</b> instruction and control returns by a RET instruction.                                                                                 | A Macro is simply accessed by <b>writing its name</b> . The entire macro code is pasted at the location by the assembler.                                                                 |

| 3 | Reduces the size of the program                                                                                                                                                | Increases the size of the program                                                                                                                                                         |

| 4 | <b>Executes slower</b> as time is wasted to push and pop the return address in the stack.                                                                                      | <b>Executes faster</b> as return address is not needed to be stored into the stack, hence push and pop is not needed.                                                                     |

| 5 | Depends on the stack                                                                                                                                                           | Does not depend on the stack                                                                                                                                                              |

# Type 1) Iteration Control Instructions

MOV BL, AL

LOOPZ BACK

```

These instructions cause a series of instructions to be executed repeatedly.

The number of iterations is loaded in CX register.

CX is decremented by 1, after every iteration. Iterations occur until CX = 0.

The maximum difference between the address of the instruction and the address of the Jump can be

127.

1) LOOP Label

Jump to specified label if CX not equal to 0; and decrement CX.

MOV CX, 40H

Eq:

BACK: MOV AL, BL

ADD AL, BL

MOV BL, AL

; Do CX ← CX - 1.

LOOP BACK

; Go to BACK if CX not equal to 0.

2) LOOPE/LOOPZ Label (Loop on Equal / Loop on Zero)

Same as above except that looping occurs ONLY if Zero Flag is set (i.e. ZF = 1)

MOV CX, 40H

Ea:

BACK: MOV AL, BL

ADD AL, BL

MOV BL, AL

; Do CX ← CX - 1.

LOOPZ BACK

; Go to BACK if CX not equal to 0 and ZF = 1.

3) LOOPNE/LOOPNZ Label (Loop on NOT Equal / Loop on NO Zero)

Same as above except that looping occurs ONLY if Zero Flag is reset (i.e. ZF = 0)

MOV CX, 40H

Eg:

BACK: MOV AL, BL

ADD AL, BL

```

; Do CX ← CX - 1.

; Go to BACK if CX not equal to 0 and ZF = 0.

# Type 2) Processor Control / Machine Control Instructions

(these are instructions that directly operate on Flag Reg)

In the exam first explain the following instructions: PUSHF, POPF, LAHF and SAHF

# For Carry Flag

1) STC

This instruction sets the Carry Flag. No Other Flags are affected.

2) CLC

This instruction clears the Carry Flag. No Other Flags are affected.

3) CMC

This instruction complements the Carry Flag. No Other Flags are affected.

# For Direction Flag

4) STD

This instruction sets the Direction Flag. No Other Flags are affected.

5) CLD

This instruction clears the Direction Flag. No Other Flags are affected.

# For Interrupt Enable Flag

6) STI

This instruction sets the Interrupt Enable Flag. No Other Flags are affected.

7) CLI

This instruction clears the Interrupt Enable Flag. No Other Flags are affected.

Note: There is no direct way to alter TF. It can be altered through program as follows:

## To set TF:

```

PUSHF ; push contents of Flag register into the stack

POP BX ; pop contents of flag reg from the stack-top into BX

OR BH, 01H ; set the bit corresponding to TF, in the BH register

PUSH BX ; push the modified BX register into the stack

POPF ; pop the modified contents into flag register.

```

## To reset TF:

```

PUSHF

POP BX

AND BH, FEH

PUSH BX

POPF

; push contents of Flag register into the stack

; pop contents of flag reg from the stack-top into BX

; reset the bit corresponding to TF, in the BH register

; push the modified BX register into the stack

; pop the modified contents into flag register.

```

## **External Hardware Synchronization Instructions** Type 3)

### 1) ESC

This is an 8086 instruction-prefix used to indicate that the current instruction is for the 8087 NDP.

We write a homogeneous program for the two processors 8086 and 8087.

Instructions are fetched by 8086 into its queue.

8087 duplicates the instruction queue of 8086 and monitors this queue.

When an instruction with ESC prefix (binary code 11011) is encountered, 8087 is activated, and hence it executes the instruction.

8086 treats the instruction as NOP.

ESC has to be written before each 8087 instruction.

## 2) WAIT

This instruction is used to synchronize 8086 with the 8087 Co-Processor via the TEST input pin of 8086. Whenever 8087 is busy it puts a "1" on its BUSY o/p line connected to the  $\overline{\text{TEST}}$  i/p of the  $\mu P$ .

The WAIT instruction makes the  $\mu P$  check the  $\overline{TEST}$  pin.

If the  $\mu P$  checks the  $\overline{\text{TEST}}$  pin and finds a "1" on it, 8086 understands that 8087 is busy and so it enters wait state. Here it does no processing.

It can come out of this idle state in 2 ways:

# TEST input is made low

i.e. 8087 is no longer busy. This takes 8086 completely out of the IDLE state.

In this case 8086 exits wait state, executes the ISR for the interrupt, and then re-enters the ii. Valid Interrupt on INTR or NMI **WAIT state**. (This is because the address of the WAIT instruction is what was pushed into the stack before executing

Thus if we write a WAIT instruction before every 8087 instruction, we can ensure that 8087 is ready for executing its own instruction whenever it arrives.

WAIT can also be written before an 8086 instruction that requires the result of a previous 8087 operation.

## 3) LOCK

This is an 8086 instruction prefix.

It prevents any external bus master from taking control of the system bus during execution of the instruction, which has a LOCK prefix.

It causes 8086 to activate the **LOCK** signal so that no other bus master takes control of the system bus. © For doubts contact Bharat Sir on 98204 08217

# 4) NOP

There is no operation performed while executing this instruction.

8086 requires 3 T-States for this instruction.

It is mainly used to insert time delays, and can also be used while debugging.

# 5) HLT

This instruction causes 8086 to stop fetching any more instructions.

8086 enters Halt state.

8086 can **come out** of this halt state only if there is a **valid hardware interrupt** (NMI or INTR) or **by reset**.

# Type 4) Interrupt Control Instructions

#### 1) INT Type

This instruction causes an interrupt of the given type. The **'Type'** can be a number between **0** ... **255**. The following action takes place:

- i. **PUSH Flag** Register onto the Stack. SP decremented by 2.

- ii. IF and TF are cleared. No other flags are affected.

- iii. PUSH CS onto the Stack. SP decremented by 2.

- iv. PUSH IP onto the Stack. SP decremented by 2. .: In all SP decremented by 6.

- v. New value of IP taken from location type x 4.

```

Eg: INT 1 ; IP \leftarrow {[00004] and [00005]} (as 1 × 4 = 00004H)

```

vi. New value of CS taken from location (type  $\times$  4) + 2.

```

Eg: INT 1 ; CS ← {[00006] and [00007]}

```

**Execution of ISR begins** from the address formed by new values of CS and IP.

#### 2) INTO (Interrupt on Overflow)

This instruction causes an interrupt of type 4, ONLY if Overflow Flag (OF) is set.

The above sequence is followed and the control is transferred to the location pointed by 00010H.

Eg: **INTO** ; If OF = 1 then execute INT 4.

Please Note: - This is INTO (O for Overflow) and NOT INT 0 (i.e. Type 0 ==> Zero Divide Interrupt).

#### 3) IRET (Return from ISR)

This instruction causes the 8086 to return to the main program from an ISR.

The following action takes place:

- i. POP IP from the Stack.

- SP incremented by 2.

- ii. **POP CS** from the Stack.

- SP incremented by 2.

- iii. POP Flag Register from the Stack.

SP incremented by 2.

.: In all SP incremented by 6.

**Execution of** the **Main Program** continues from the address formed values of CS and IP restored from the stack.

**Please Note**:- The original value of TF and IF are restored from the Stack. Also note that to come back from an ISR, the programmer must use the IRET instruction and not the normal RET instruction as the RET instruction will not POP back the Flag.

#### String Instructions of 8086 (Very Important × 10m) Type 5)

A String is a series of bytes stored sequentially in the memory. String Instructions operate on such "Strings".

The Source String is at a location pointed by SI in the Data Segment.

The Destination String is at a location pointed by DI in the Extra Segment.

The Count for String operations is always given by CX.

Since CX is a 16-bit register we can transfer max 64 KB using a string instruction.

SI and/or DI are incremented/decremented after each operation depending upon the direction flag "DF" in the flag register.

If **DF = 0**, it is **auto increment**. This is done by **CLD instruction**. If DF = 1, it is auto decrement. This is done by STD instruction.

# 1)MOVS: MOVSB/MOVSW (Move String)

It is used to transfer a word/byte from data segment to extra segment.

The offset of the source in data segment is in SI.

The offset of the destination in extra segment is in DI.

SI and DI are incremented / decremented depending upon the direction flag.

```

; ES:[DI] ← DS:[SI] ... byte transfer

Eg:

MOVSB

; SI \leftarrow SI \pm 1 ... depending upon DF

; DI ← DI ± 1 ... depending upon DF

; {ES:[DI], ES:[DI + 1]} ← {DS:[SI], DS:[SI + 1]}

MOVSW

; SI \leftarrow SI \pm 2

; DI ← DI ± 2

```

# 2)LODS: LODSB/LODSW (Load String)

It is used to Load AL (or AX) register with a byte (or word) from data segment.

The offset of the source in data segment is in SI.

SI is incremented / decremented depending upon the direction flag (DF).

```

; AL 	DS:[SI] ... byte transfer

LODSB

Eq:

; SI ← SI ± 1 ... depending upon DF

; AL ← DS:[SI]; AH ← DS:[SI + 1]

LODSW

; SI ← SI ± 2

```

# 3)STOS: STOSB/STOSW (Store String)

It is used to Store AL (or AX) into a byte (or word) in the extra segment.

The offset of the source in extra segment is in DI.

DI is incremented / decremented depending upon the direction flag (DF).

Eg: STOSB ; ES:[DI] ← AL ... byte transfer