## SELETRXITE (Rev.) 21/5/2012 Digital System Design I

PH March Exam (4) 129

Con. 3790-12.

GN-5519

(3 Hours)

Total Marks: 100

- N.B. (1) Question No. 1 is compulsory.

- (2) Answer any four questions out of remaining six questions.

- (3) Figures to the right indicates full marks.

- (4) Assumptions made must be clearly stated.

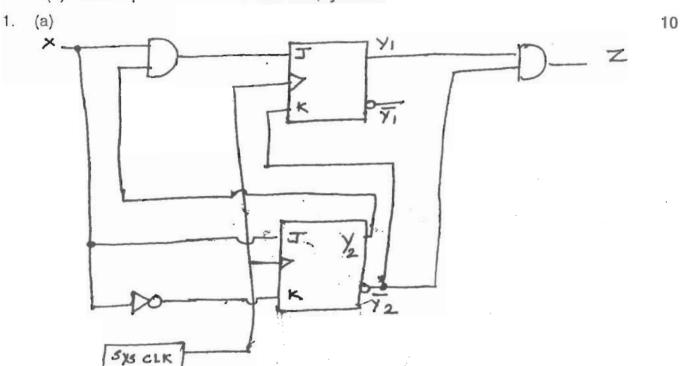

Analyze the sequential M/c and draw the state diagram.

- (b) Write V.H.D.L. code for full adder using half adder as component.

- 10

- (a) Write behavioural description code of simple 11 bit floating point encoder.

(b) Write a V.H.D.L. code for multiplexer IC 74151.

- 10

10

(a) Reduce the state table using implication chart method and design state machine 10 using D F/F and decoder.

| Present state - | Next state     |                | O/P (z) |       |

|-----------------|----------------|----------------|---------|-------|

|                 | x = 0          | x = 1          | x = 0   | x = 1 |

| So              | S <sub>4</sub> | S <sub>3</sub> | 0       | 1     |

| S <sub>1</sub>  | S <sub>5</sub> | S <sub>3</sub> | 0       | 0     |

| S <sub>2</sub>  | S              | S,             | 0       | 1     |

| S <sub>3</sub>  | S <sub>5</sub> | S,             | 0       | 0     |

| S <sub>4</sub>  | S <sub>2</sub> | S <sub>5</sub> | 0       | 1     |

| S <sub>5</sub>  | S,             | S <sub>2</sub> | 0       | 0     |

4. (a) Design a Moore sequential machine that detects serial I/P of 010110.

Use suitable F/F's and logic for designing.

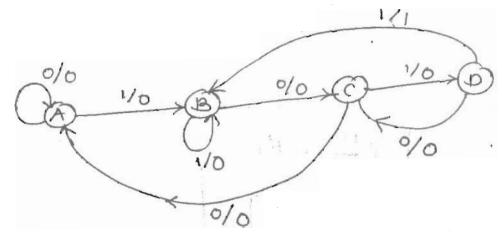

(b) Describe a State Machine shown below in V.H.D.L.

10

- (a) Design a coin operated vending machine that dispenses Candy under the following conditions—

- (i) The machine accepts ₹ 5 and ₹ 10 coins.

- (ii) It takes ₹ 15 for one piece of candy to be released from the mac ane.

- (iii) If ₹ 20 is deposited the machine will credit the buyer with ₹ 5 and wait for the buyer to make second purchase.

Design using Mealy Machine.

- (b) Design MOD 193 counter with the counting sequence . . . . . 63, 64, 65, . . . . . . 10 254, 255, 63, 64, . . . . . use IC 74163.

- (a) Draw and explain Logic diagram of 64 x 1 diode ROM.

Use 2-dimensional decoding.

- (b) Write V.H.D.L. code for JK F/F. Use Asynchronous preset and synchronous clear. 10

- 7. (a) Explain the working of CPLD XC 9500 in detail.

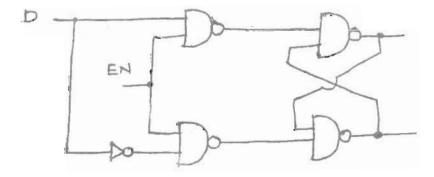

- (b) Analyze the pulse mode asynchronous sequential machine and obtain the state 10 diagram.