# AC Unit - 1

- Introduction Recap of Small Signal Amplifiers

- Multistage Amplifiers, Cascode amplifier

- Darlington pair

- the MOS Differential Pair

- > Small-Signal Operation of the MOS Differential Pair

- > The BJT Differential Pair

- > Nonideal Characteristics of the Differential Amplifier.

## **AMPLIFIER:**

A circuit that increases amplitude of given signal is an amplifier. The amplifier is an electronic circuit, which **amplifies or increases strength of weak signal**.

- > A small AC signal fed into amplifier is obtained as large AC signal of same frequency.

- > A amplifier is essential part in radios, TV's and other communications

A linear amplifier magnifies an input signal and produces an output signal whose magnitude is larger and directly proportional to the input signal.

The ac analysis, called a small-signal analysis, can be performed with the dc source set to zero.

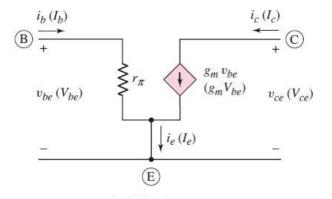

### Small-Signal Hybrid- $\pi$ Equivalent Circuit of the Bipolar Transistor

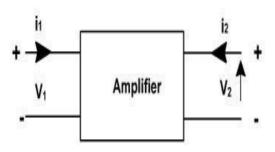

All the transistor amplifiers are two port networks having two voltages and two currents. The positive directions of voltages and currents.Out of four variables two can be selected as are independent variables and two are dependent variables.

#### In h- parameters

- (V<sub>1</sub> & I<sub>2</sub>) Dependent Variables

- > (I<sub>1</sub> & V<sub>2</sub>) Independent Variables

Time

$v_{RF}$

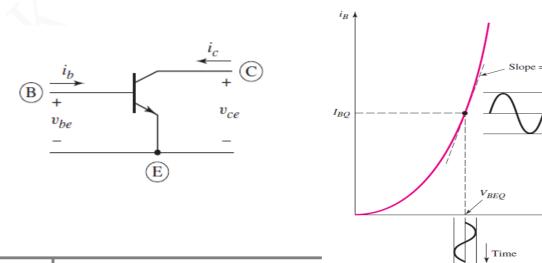

Assuming the transistor as two port network. The  $i_B vs v_{BE}$  graph the small time varying signal is superimposed on Q-point. The slope of Q-point is constant with units of conductance.

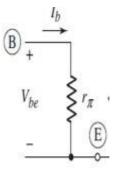

The inverse of this conductance is the small-signal resistance defined as  $r_{\pi}$

$$V_{be} = i_b r_{\pi}$$

By using above equation we have to draw input port

then

Q-pt

The resistance  $r_{\pi}$  is called the **diffusion resistance** or base–emitter input resistance •

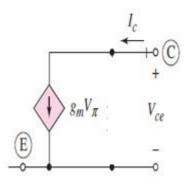

For Output Collector–Emitter Port

Assuming the collector current is independent of  $V_{CE}$

$$\Delta i_{C} = \frac{\partial i_{C}}{\partial v_{BE}} |_{Q-pt} \cdot \Delta v_{BE}$$

or  $i_{C} = \frac{\partial i_{C}}{\partial v_{BE}} |_{Q-pt} \cdot v_{BE}$  ---1

$i_{C} = k \exp\left(\frac{v_{BE}}{v_{T}}\right)$

$\frac{\partial i_{C}}{\partial v_{BE}} |_{Q-pt} = \frac{1}{v_{T}} \left[ I_{S} \cdot \exp\left(\frac{v_{BE}}{v_{T}}\right) \right] |_{Q-pt} = \frac{I_{CQ}}{v_{T}}$

$g_{m} = \frac{I_{CQ}}{v_{T}}$   $\therefore$  Which is called Transconductance

$\frac{\partial i_{C}}{\partial v_{BE}} |_{Q-pt} = g_{m}$  ---2

Substitute equation 2 in 1

We can then write the small-signal collector current as

$$i_c = g_m V_{be}$$

By using above equation we have to draw output port

Combine input port an output port, we will get small signal Hybrid- $\pi$  Equivalent Circuit of the Bipolar Transistor

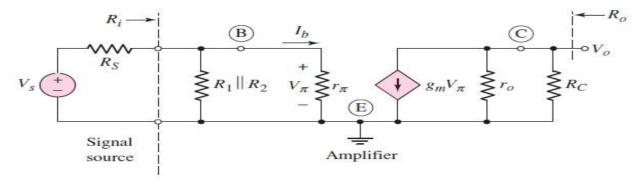

Fig: A simplified small-signal hybrid- $\pi$  equivalent circuit

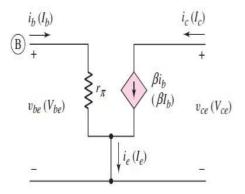

#### **Alternative Form of Equivalent Circuit**

$$ic = \frac{\partial ic}{\partial i_B} |_{Q-pt} \cdot i_B$$

where

$$\frac{\partial i_{c}}{\partial i_{B}} = \beta$$

We can then write as  $i_c = Q i_b$

$$r_{\pi}g_{m} = \begin{bmatrix} \underline{QV_{T}} \\ I_{CQ} \end{bmatrix} \begin{bmatrix} \underline{I_{CQ}} \\ V_{T} \end{bmatrix} = \mathbf{Q}$$

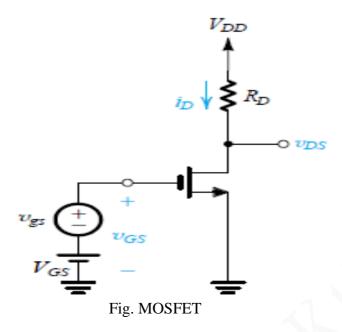

## **Small-Signal Equivalent-Circuit Models:**

- > The FET behaves as a voltage-controlled current source.

- ➤ It accepts a signal v<sub>gs</sub> between gate and source and provides a current g<sub>m</sub>v<sub>gs</sub> at the drain terminal.

- > The input resistance of this controlled source is very high and ideally infinite.

- The output resistance looking into the drain also is high, and we have assumed it to be infinite.

The DC bias current is  $I_D = \frac{1}{2} k'_n \frac{W}{L} (V_{gs} - V_t)^2$

$k'_n = \mu_n C_{OX}$

```

V_{OV} = V_{GS} - V_t is the overdrive voltage at which the MOSFET is biased to operate.

```

$$g_{m} = k'_{n \frac{W}{L}} (V_{gs} - V_{t}) = k'_{n \frac{W}{L}} V_{OV}$$

$$g_{n} = \frac{2I_{D}}{V_{gs} - V_{t}} = \frac{2I_{D}}{V_{OV}}$$

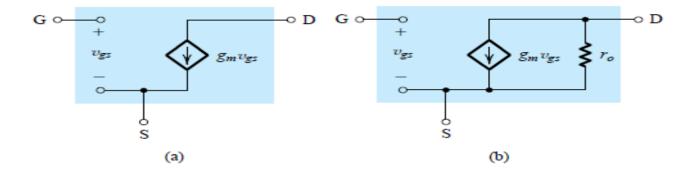

The small-signal model of the MOSFET

Fig. Small-signal models for the MOSFET: (a) neglecting the dependence of  $i_D$  on  $v_{DS}$  in saturation (b) including the effect of channel-length modulation, modeled by output resistance

$$g_{m} = k'_{n} \frac{W}{L} (V_{gs} - V_{t}) = k'_{n} \frac{W}{L} V_{OV} \qquad r_{o} = \frac{|V_{A}|}{I_{D}}$$

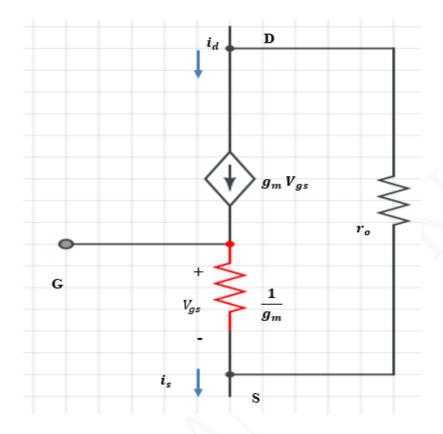

#### **MOSFET T equivalent –circuit model**

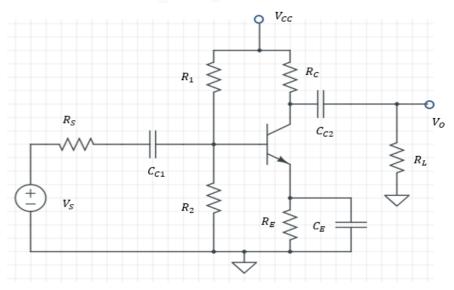

**Common Emitter Amplifier: (CE Amplifier)**

- V<sub>s</sub> = Signal Source

- R<sub>s</sub> = Source Resistance

- C<sub>c</sub> = Coupling capacitor

- $R_1 \& R_2 = Self bias$

- R<sub>c</sub>= Load

- V<sub>cc</sub> = DC Supply Voltage

- V<sub>o</sub> = output voltage

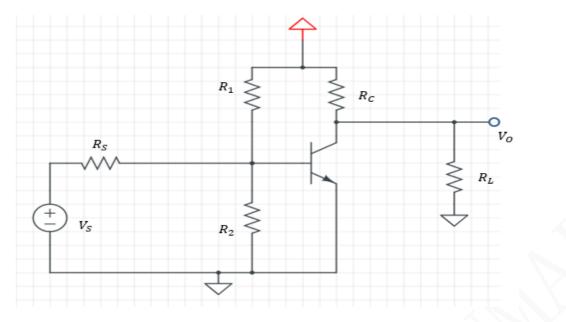

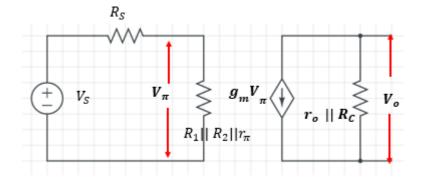

For AC(mid frequency) analysis all external capacitors are short circuit.

$g_m V_\pi$

$R_1 || R_2 || r_{\pi}$

$$V_0 = -g_m V_\pi[r_0||R_C]$$

And the control voltage  $V_{\pi}$  is found to be

$$V_{\pi} = \frac{R_1 ||R_2||r_{\pi}}{(R_1||R_2||r_{\pi}) + R_s} V_s \qquad ---2$$

Substitute eq2 in eq1

$$V_{O} = -g_{m} \frac{R_{1} ||R_{2}||r_{\pi}}{(R_{1}||R_{2}||r_{\pi}) + R_{s}} V_{S} \begin{bmatrix} r \\ o \end{bmatrix} = 0$$

----1

$$A_{V} = \frac{V_{o}}{V_{s}} = -g_{m} [r_{o}||R_{c}] [\frac{R_{1}||R_{2}||r_{\pi}}{(R_{1}||R_{2}||r_{\pi}) + R_{s}}]$$

Assume  $R_1||R_2||r_{\pi} = R_B$  and  $r_o||R_c = R_c$

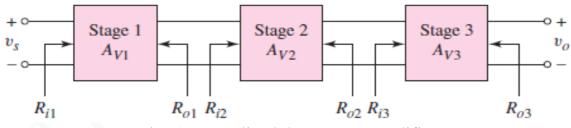

#### Multistage amplifiers:

- ➤ In practical applications, the output of a single state amplifier is usually insufficient, though it is a voltage or power amplifier. Hence they are replaced by Multistage amplifiers.

- ➤ A generalized three-stage amplifier is shown in below figure.

Fig. A generalized three-stage amplifier

- In Multi-stage amplifiers, the output of first stage is coupled to the input of next stage using a coupling device. These coupling devices can usually be a capacitor or a transformer. This process of joining two amplifier stages using a coupling device can be called as Cascading.

- In general, the input impedance of the first stage must be high and the output impedance of the last must be low.

- > The overall gain is the product of the individual gains.

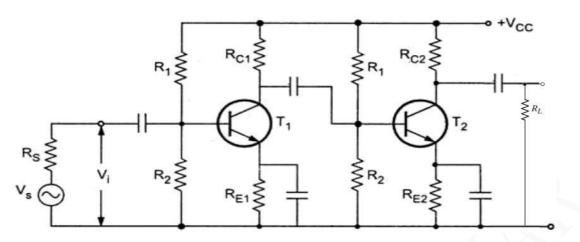

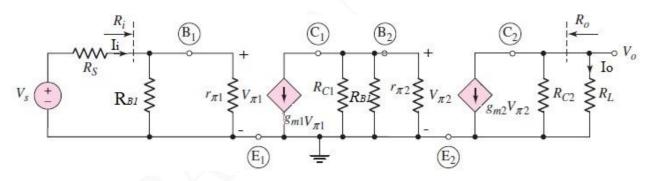

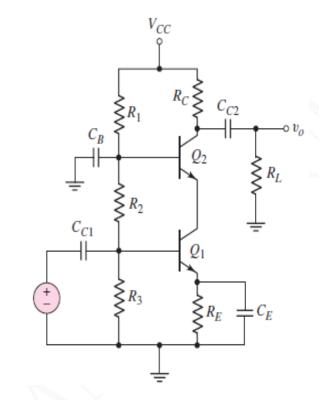

Two stage RC coupled CE-CE cascade amplifier:

Fig. Two stage RC coupled CE-CE cascade amplifier

## AC analysis of the amplifier circuit:

Fig shows the small-signal equivalent circuit, assuming all capacitors act as short circuits, DC sources set to zero and each transistor output resistance r<sub>o</sub> is infinite.

Fig. Small-signal equivalent circuit of the cascade circuit

- The bias resistance of the amplifier is  $R_{B1} = R_1 \parallel R_2$

- The input resistance of the amplifier is  $R_i = R_{B1} \parallel r_{\pi 1}$

- The out resistance of the amplifier is  $R_o = R_{C2}$

The Voltage gain of the amplifier is

$$A_{VS} = \frac{V_{O}}{V_{S}} = g_{m1} g_{m2} R_{C2} \| R_{L} (R_{a} \| R_{B1} \| r_{\pi 2}) \frac{R_{i}}{R_{i} + R_{s}}$$

The current gain of the amplifier is

$$A_{IS} = \frac{I_0}{I_i} = g_{m1}g_{m2}(R_{C1} \parallel R_{B1} \parallel r_{\pi 2})r_{\pi 1}(\frac{R_{C2}}{R_{C2} + R_L})(\frac{R_{B1}}{R_{B1} + r_{\pi 1}})$$

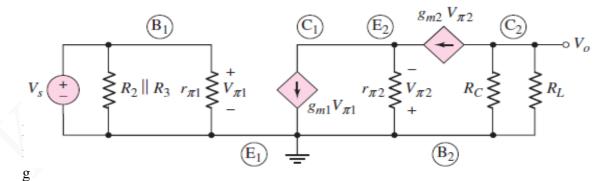

# **Cascode Amplifier :**

Cascode amplifier is a type of multistage amplifier. The CE amplifier followed by CB amplifier is called cascode amplifier. The high bandwidth and high gain are major advantages of cascode amplifier. The input is into a common-emitter amplifier ( $Q_1$ ), which drives a common-base amplifier ( $Q_2$ ). The output signal current of  $Q_1$  is the input signal of  $Q_2$ .

Fig. Cascode amplifier

. Small-signal equivalent circuit of the cascode amplifier

The bias resistance of the amplifier is  $R_{B1} = R_2 \parallel R_3$

The input resistance of the amplifier is  $R_i = R_{B1} \parallel r_{\pi 1}$

The out resistance of the amplifier is  $R_o = R_c$

$V_{\pi 1} = V_s$  since we are assuming an ideal signal voltage source.

The Voltage gain of the amplifier is

The output voltage is

Writing a KCL equation at E<sub>2</sub>, we have

$$g_{m1}V_{\pi 1} = \frac{V_{\pi 2}}{r_{\pi 2}} + g_{m2}V_{\pi 2}$$

The control voltage  $V_{\pi 2}~$  (noting that  $V_{\pi 1}=V_s$  ), we find

$$V_{\pi 2} = g_{m1}V_{s}r_{\pi 2} - g_{m2}V_{\pi 2}r_{\pi 2}$$

$$V_{\pi 2} + g_{m2}V_{\pi 2}r_{\pi 2} = g_{m1}V_{s}r_{\pi 2}$$

$$V_{\pi 2}(1 + g_{m2}r_{\pi 2}) = g_{m1}V_{s}r_{\pi 2}$$

$$V_{\pi 2} = \frac{g_{m1}V_{s}r_{\pi 2}}{(1 + g_{m2}r_{\pi 2})}$$

$$\therefore \beta_{2} = g_{m2}r_{\pi 2}$$

$$V_{\pi 2} = (\frac{r_{\pi 2}}{1 + \beta_{2}})g_{m1}V_{s}$$

---3

Substitute eq. (3) in eq. (2), we get output voltage as

$$V_o = -g_{m1}g_{m2}\left(\frac{r_{m2}}{1+\beta_2}\right)g_{m1}V_s\left[R_c \parallel R_L\right]$$

Therefore, the small-signal voltage gain is

$$A_{vs} = \frac{V_o}{V_s} = -g_{m1}g_{m2}\left(\frac{r_{\pi 2}}{1+Q_2}\right)g_{m1}\left[R_c \parallel R_L\right]$$

We know that  $g_{m2}\left(\frac{r_{\underline{n}2}}{1+\beta_2}\right) = \frac{\beta}{1+\beta_2} \cong 1$

The gain of the cascode amplifier is then approximately

$$A_{vs} \cong -g_{m1} \left[ R_c \parallel R_L \right]$$

Which is the same as for a single-stage common-emitter amplifier.

The current gain of the amplifier is  $A_{IS} = \frac{I_0}{I_s}$

The output current is

$$I_{0} = -g_{m2}V_{\pi 2} \left(\frac{R_{C}}{R_{C} + R_{L}}\right) \qquad - - - - - - (4)$$

But we know that

$$V_{\pi 2} = \frac{r_{\pi 2}}{1 + \beta_2} g_{m1} V_s \quad - - - -(5)$$

Substitute eq.(5) in eq.(4), we get

$$I_0 = -g_{m2} \left(\frac{R_C}{R_C + R_L}\right) \frac{r_{\pi 2}}{1 + \beta_2} g_{m1} V_s \quad ---(6)$$

We know that

$$V_s = I_s R_i \quad ---(7)$$

Substitute eq.(7) in eq.(6) we get

$$I_{O} = -g_{m2} \left( \frac{R_{C}}{R_{C} + R_{L}} \right) \frac{r_{\pi 2}}{1 + \beta_{2}} g_{m1} I_{s} R_{i}$$

The current gain of the amplifier is

$$A_{IS} = \frac{I_0}{I_i} = -g_{m1}g_{m2} \left(\frac{r_{\pi 2}}{1+Q_2}\right) \left(\frac{R_C}{R_C+R_L}\right) R_i$$

We know that  $g_{m2}\left(\frac{r_{n2}}{1+\beta_2}\right) = \frac{\beta}{1+\beta_2} \cong 1$

$$A_{IS} = -g_{m1} \left( \frac{R_C}{R_C + R_L} \right) R_i$$

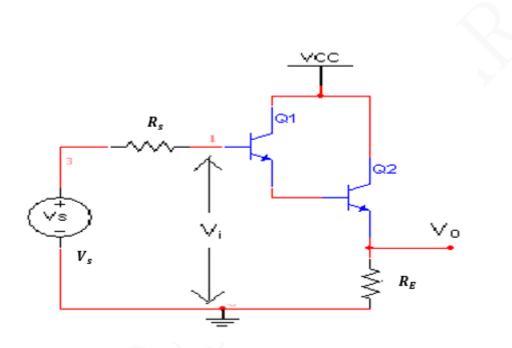

## **Darlington Pair amplifier:**

- > The Darlington pair invented at Bell by the engineer Darlington in 1953

- The main advantage of Darlington pair is the composite transistor act as a single transistor with high current gain.

- > The darlington pair made up with two transistors of current gain  $\beta 1$ ,  $\beta 2$

- > The overall current gain of darrlington pair is multiplication of individual current gains.

- If matched transistors then  $\beta 1 = \beta 2$  then  $\beta_d = \beta 1^2$

- Generally darlington pair available in package contain 3 terminals i.e. base ,emitter ,and collector

- Darlington pair can be used as emitter follower its equivalent is cascading of two emitter followers.

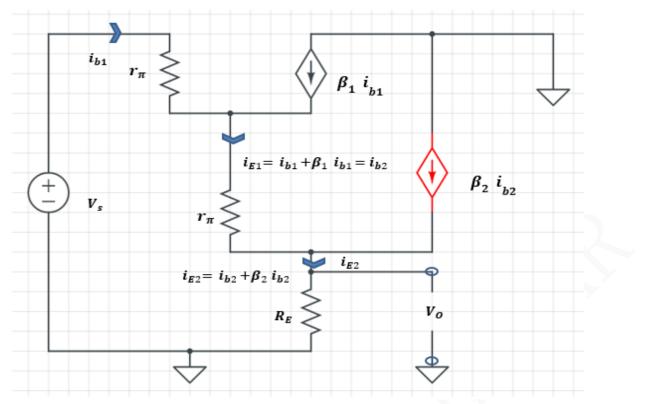

Fig: A Darlington pair amplifier or configuration

The Darlington pair basically consisting of two bipolar transistors with the emitter of one transistor connected to the base of the other, such that the current amplified by the first transistor is amplified further by the second one.

The collectors of both transistors are connected together. It is often packaged as a single transistor. The high current gain and high input impedance are the advantages of Darlington pair. One drawback is doubling of the base–emitter voltage.

Fig: Small-signal equivalent circuit of Darlington pair

$$i_{E1} = i_{b1} + \beta_1 i_{b1} = i_{b1} [1 + \beta_1] = i_{b2}$$

----1

$$i_{E2} = i_{b2} + \beta_1 i_{b2} = i_{b2} [1 + \beta_2] ---2$$

Substitute equation 1 in 2

$$i_{E2} = i_{b2}[1 + \beta_2] = i_{b1}[1 + \beta_1][1 + \beta_2]$$

### Current gain

$$A_{I} = \frac{i_{E2}}{i_{b1}} = \frac{i_{b1}[1+\beta_{1}][1+\beta_{2}]}{i_{b1}}$$

$$A_{I} = [1+\beta_{1}][1+\beta_{2}] \qquad \therefore \beta_{1} \gg 1, \beta_{2} \gg 1$$

$$A_{I} = \beta_{1}\beta_{2} \qquad \therefore \text{ identical transistors } \beta_{1} = \beta_{2}$$

$$A_{I} = Q_{1}^{2} = Q_{2}^{2} = Q_{D}$$

#### Voltage gain

$$A_{V} = \frac{V_{O}}{V_{S}} = \frac{i_{E2}R_{E}}{V_{S}} = \frac{i_{b1}[1+\beta_{1}][1+\beta_{2}]R_{E}}{V_{S}} ---4$$

Apply KVL for input loop

$$V_S = i_{b1} r_{\pi 1} + i_{b2} r_{\pi 2} + i_{E2} R_E$$

----5

----3

$$V_{S} = ib_{1} r_{n1} + ib_{1} [1 + \beta_{1}] r_{n2} + ib_{1} [1 + \beta_{2}] R\varepsilon$$

$$V_{S} = ib_{1} [r_{n1} + [1 + \beta_{1}] r_{n2} + [1 + \beta_{1}] [1 + \beta_{2}] R\varepsilon$$

$$V_{S} = ib_{1} [r_{n1} + \beta_{1} r_{n2} + \beta_{1} ] \qquad \therefore r_{n1} \ll \beta_{1} r_{n2} \qquad \therefore r_{n2} = \frac{\beta_{2}}{g_{m}}$$

$$V_{S} = ib_{1} [\beta_{1} \frac{\beta_{2}}{g_{m}} + \beta_{1} \beta_{2} \frac{\beta_{2}}{\varepsilon}] \qquad \therefore \beta_{1} \beta_{2} = \beta_{D}$$

$$V_{S} = ib_{1} \beta_{D} [\frac{1}{g_{m}} + \beta_{1} R\varepsilon]$$

$$V_{S} = ib_{1} \beta_{D} [\frac{1}{g_{m}} + R\varepsilon] \qquad \qquad \cdots -6$$

Substitute equation 6 in 4

$$A_{V} = \frac{ib_{1} \beta_{D} \frac{1}{g_{m}^{-1} + R\varepsilon]}{ib_{1} \beta_{D} \frac{1}{g_{m}^{-1} + R\varepsilon]}} \qquad \therefore \beta_{1} \beta_{2} = \beta_{D}$$

$$A_{V} = \frac{-ib_{1} \beta_{D} \frac{1}{g_{m}^{-1} + R\varepsilon]}{ib_{1} \beta_{D} \frac{1}{g_{m}^{-1} + R\varepsilon]}}$$

$$A_{V} = \frac{-ib_{1} \beta_{D} \frac{R\varepsilon}{g_{m}^{-1} + R\varepsilon]}}{ib_{1} \beta_{D} \frac{1}{g_{m}^{-1} + R\varepsilon]}} \qquad \therefore \frac{1}{g_{m}} \ll R_{E}$$

$$A_{V} = \frac{R\varepsilon}{[\frac{1}{g_{m}} + R\varepsilon]}$$

$$Z_{i} = \frac{\Psi_{S}}{I_{b1}} = \frac{\frac{i_{b1}\beta_{D}\left[\frac{1}{g_{m}} + R_{E}\right]}{g_{m}}}{I_{b1}}$$

$$Z_{i} = Q_{D}\left[\frac{1}{g_{m}} + R_{E}\right]$$

Output impedance

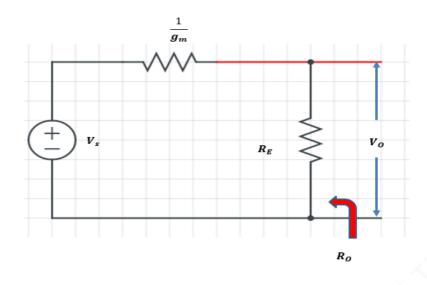

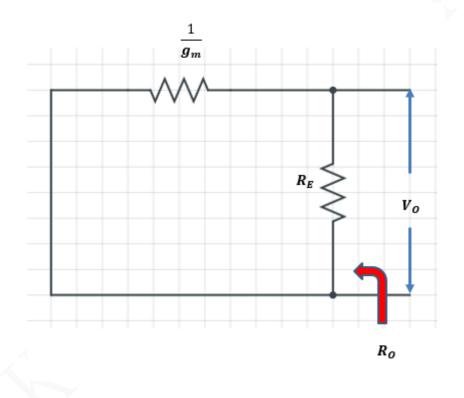

$$A_{V} = \frac{V_{O}}{V_{S}} = \frac{R_{E}}{\frac{1}{g_{m}} + R_{E}}}$$

$$V_{O} = \frac{R_{E}}{\frac{1}{g_{m}} + R_{E}}}V_{S}$$

---1

Equation 1 convert to equivalent circuit

For calculating output impedance  $V_s = 0$ , the above circuit simplified to

$Zo = \frac{1}{g_m} ||R_E|$

: Low resistance || high resistance

$$\cong$$

Low resistance  $\therefore \frac{1}{g_m} \ll R_E$

$$Z_0\cong rac{1}{g_m}$$

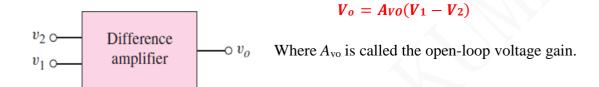

## **Differential pair or Amplifier:**

- The differential-pair or differential-amplifier is the most widely used building block in analog integrated-circuit design. For instance, the input stage of every op-amp is a differential amplifier.

- The BJT differential amplifier is the basis of a very-high-speed logic circuit family like emittercoupled logic (ECL).

- Differential Amplifiers is an amplifier in which the output voltage is directly proportional to the difference of input signal. This amplifier, also called a diff-amp

There are two input terminals and one output terminal

The differential-mode input voltage  $V_d = V_1 - V_2$

The common-mode input voltage  $V_{cm} = \frac{V_1 \pm V_2}{2}$

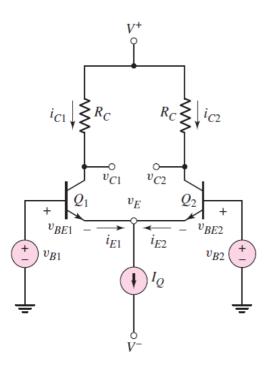

#### The BJT Differential Pair:

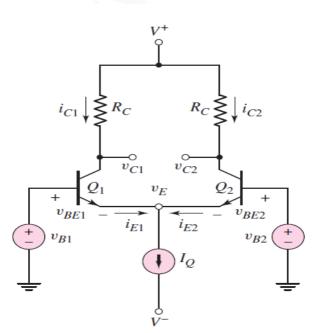

• The basic BJT differential pair is shown in fig.

Fig. The basic BJT differential pair

> It consists of two identical transistors  $Q_1$  and  $Q_2$ , whose emitters are joined together and biased by a constant-current source  $I_Q$ . Each collector is connected to the  $V_{CC}$  through a resistance  $R_C$ . The two transistors must be operated in active region.

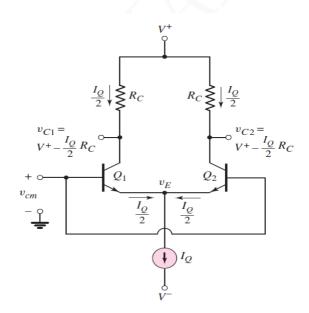

#### **Basic Operation of the BJT differential pair:** case (I): $v_{B1} = v_{B2} = V_{CM}$

- Let us consider the first case where the two bases joined together and connected to a commonmode voltage V<sub>CM</sub> as shown in fig.(a) and  $v_{B1} = v_{B2} = V_{CM}$ .

- Since Q<sub>1</sub> and Q<sub>2</sub> are matched, the current I will divide equally between the two transistors. Thus,  $i_{E1} = i_{E2} = I/2$ . The voltage at the emitters will be  $V_{CM} - V_{BE}$

- ▶ Where  $V_{BE} = 0.7$  V

- > The voltage at each collector will be  $V_{CC} \frac{\alpha l}{2} R_C$

$I_{E1} = I_{E2} = \frac{\alpha I_Q}{2} \qquad \therefore \text{ If the base currents are negligible } I_{C1} = I_{E1}, I_{C2} = I_{E2}$  $V_{C1} = V_{CC} - \frac{\alpha I}{2} R_C = V_{C2} \qquad \qquad \frac{\alpha I_Q}{2} \cong \frac{I_Q}{2}$  $V_o = V_{C2} - V_{C1} = \mathbf{0}$

The difference in voltage between the two collectors will be zero. Thus the differential pair does not respond to (i.e., it rejects) to the common-mode input voltage.

Fig: The differential pair with a common-mode input voltage

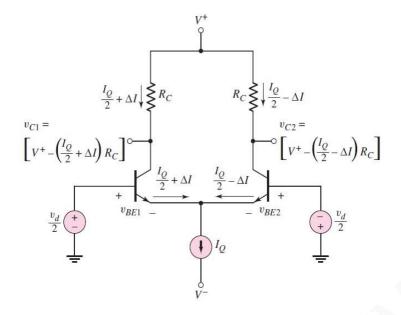

**Case II:** if  $V_{B1}$  increases by a few millivolts and  $V_{B2}$  decreases by the same amount.

$V_{BE1} > V_{BE2}$ , which means that  $i_{C1}$  increases by  $\Delta I$  above its quiescent value and  $i_{C2}$  decreases by  $\Delta I$  times

Fig: Differential pair with a small differential input signal

- From Fig, It can be seen that we are able to steer the entire bias current from one side of the pair to the other with small difference voltages. This current steering property of the differential pair allows it to be used in logic circuits.

- > Apply a very small differential signal, which will result in one of the transistors conducting a current of  $\frac{I}{2} + \Delta I$ ; the current in the other transistor will be  $\frac{I}{2} \Delta I$ ...

$$V_o = V_{c2} - V_{c1} = \left[V_{cc} - \left(\frac{I_Q}{2} - \Delta I\right)R_c\right] - \left[V_{cc} - \left(\frac{I_Q}{2} + \Delta I\right)R_c\right] = 2\Delta IR_c$$

A voltage difference is created between  $v_{C2}$  and  $v_{C1}$  when a differential-mode input voltage is applied.

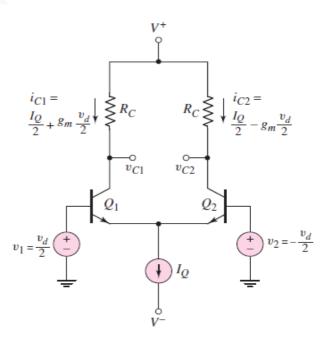

The magnitude of the small-signal collector current in each transistor is then  $(g_m v_d)/2$ .

$$V_{o} = V_{C2} - V_{C1}$$

$$V_{o} = [V_{CC} - I_{C2}R_{C}] - [V_{CC} - I_{C1}R_{C}] = (I_{C1} - I_{C2})R_{C}$$

$$V_{o} = [(\frac{I_{Q}}{2} + \frac{g_{m}V_{d}}{2}) - (\frac{I_{Q}}{2} - \frac{g_{m}V_{d}}{2})]R_{C}$$

$$V_{o} = g_{m}V_{d}R_{C}$$

#### **Differential mode gain:**

The ratio of the output signal voltage to the differential-mode input signal is called the differential-mode gain, *Ad*, which is

$V_o = g_m V_d R_c$

$$A_d = \frac{V_o}{V_d} = g_m R_c$$

$\therefore \mathcal{G}_m = \frac{I_C}{V_T} = \frac{\frac{I_Q}{2}}{V_T} = \frac{I_Q}{2V_T}$

In many cases output is taken at one collect terminal which is called a one-sided output

$V_o = \frac{\underline{a}_m \underline{V}_d \underline{R}_c}{2}$  $A_d = \frac{\underline{a}_m \underline{R}_c}{2}$

∴ For Unbalanced output /Single output

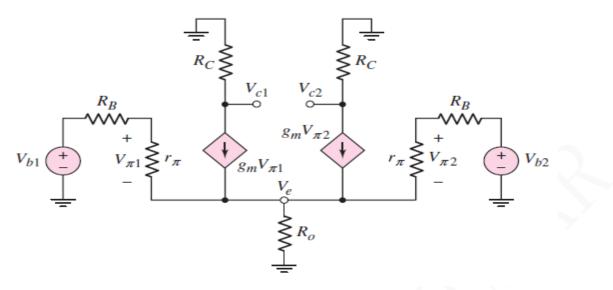

## Small signal analysis of BJT differential pair

The small signal equivalent circuit of differential amplifier is given as

Assuming the transistors are identical, so  $r_{\pi 1} = r_{\pi 2} \equiv r_{\pi}$  and  $g_{m1} = g_{m2} \equiv g_m$

Apply KCL at node

$$V_e$$

$\frac{V_{\pi 1}}{r_{\pi}} + g \bigvee_{m \pi 1} + g \bigvee_{m \pi 2} + \frac{V_{\pi 2}}{r_{\pi}} = \frac{V_e}{R_o}$  ---1

$V_{\pi 1} [\frac{1}{r_{\pi}} + g_m] + V_{\pi 1} [\frac{1}{r_{\pi}} + g_m] = \frac{V_e}{R_o}$

$V_{\pi 1} [\frac{1+g_m r_{\pi}}{r_{\pi}}] + V_{\pi 1} [\frac{1+g_m r_{\pi}}{r_{\pi}}] = \frac{V_e}{R_o}$

$V_{\pi 1} [\frac{1+\beta}{r_{\pi}}] + V_{\pi 1} [\frac{1+\beta}{r_{\pi}}] = \frac{V_e}{R_o}$  ---2

From the circuit

$$\frac{V_{\pi 1}}{r_{\pi}} = \frac{V_{b1} - V_{e}}{r_{\pi} + R_{B}} \quad and \quad \frac{V_{\pi 2}}{r_{\pi}} = \frac{V_{b2} - V_{e}}{r_{\pi} + R_{B}}$$

$$V_{\pi 1} = \Re \left[ \frac{V_{b1} - V_{e}}{r_{\pi} + R_{B}} \right] and \quad V_{\pi 2} = \Re \left[ \frac{V_{b2} - V_{e}}{r_{\pi} + R_{B}} \right]$$

Substituting  $V_{\pi 1}$ ,  $V_{\pi 2}$  in equation 2

$$r_{\pi} \begin{bmatrix} \frac{V_{b1} - V_{e}}{r_{\pi} + R_{B}} \end{bmatrix} \begin{bmatrix} \frac{1+\beta}{r_{\pi}} \end{bmatrix} + r_{\pi} \begin{bmatrix} \frac{V_{b2} - V_{e}}{r_{\pi} + R_{B}} \end{bmatrix} \begin{bmatrix} \frac{1+\beta}{r_{\pi}} \end{bmatrix} = \frac{V_{e}}{R_{o}}$$

$$\begin{bmatrix} \frac{1+\beta}{r_{\pi} + R_{B}} \end{bmatrix} \begin{bmatrix} V_{b1} + V_{b2} - 2V_{e} \end{bmatrix} = \frac{V_{e}}{R_{o}}$$

$$\begin{bmatrix} V_{b1} + V_{b2} - 2V_{e} \end{bmatrix} = \frac{V_{e}}{R_{o}} \begin{bmatrix} \frac{r_{\pi} + R_{B}}{1+\beta} \end{bmatrix}$$

$$\begin{bmatrix} V_{b1} + V_{b2} \end{bmatrix} = \frac{V_{e}}{R_{o}} \begin{bmatrix} \frac{r_{\pi} + R_{B}}{1+\beta} \end{bmatrix} + 2V_{e}$$

$$\begin{bmatrix} V_{b1} + V_{b2} \end{bmatrix} = \begin{bmatrix} \begin{bmatrix} r_{\pi} + R_B \\ (1+\beta)R_o \end{bmatrix} + 2 \end{bmatrix} V_{e}$$

$$V_e = \frac{[V_{b1} + V_{b2}]}{[[\frac{r_{\pi} + R_B}{(1+\beta)R_0}] + 2]} ---3$$

If we consider a one-sided output at the collector of  $Q_2$ , then

$$V_o = V_{C2} = -(g_m V_{\pi 2}) R_C = -\beta R_C \left[ \frac{V_{b2} - V_e}{r_{\pi} + R_B} \right] ---4$$

Substitute eq3 in eq4

$\therefore g_n V_{\pi} = k = \beta I_b \quad \therefore i_{b2} = \begin{bmatrix} \frac{V_{b2} - V_e}{r_{\pi} + R_B} \end{bmatrix}$

$$V_{o} = \frac{-\beta R_{C}}{r_{\pi} + R_{B}} \left[ V_{b2} - \frac{[V_{b1} + V_{b2}]}{[[\frac{r_{\pi} + R_{B}}{(1 + \beta)R_{o}}] + 2]} \right]$$

$$V_{o} = \frac{-\beta R_{C}}{r_{\pi} + R_{B}} \left[ \frac{\frac{2V_{b2} + V_{b2} \left[\frac{r_{\pi} + R_{B}}{(1+\beta)R_{o}}\right] W_{b1} - V_{b2}}{\left[\left[\frac{r_{\pi} + R_{B}}{(1+\beta)R_{o}}\right] + 2\right]} \right]$$

$$V_{o} = \frac{-QR_{c}}{r_{\pi} + R_{B}} \left\{ \frac{V_{b2} \left[ \begin{bmatrix} \frac{r_{\pi} \pm R_{B}}{1} & b_{1} \\ \frac{r_{\pi} \pm R_{B}}{1} \end{bmatrix} - V_{b2} \right]}{\begin{bmatrix} \frac{r_{\pi} \pm R_{B}}{1} \end{bmatrix} + 2} \right\} - \dots 5$$

In an ideal constant-current source, the output resistance is  $Ro = \infty$ , and above Equation reduces to

$$V_o = \frac{-\beta R_c [V_{b2} - V_{b1}]}{2(r_{\pi} + R_B)}$$

The differential-mode input is  $V_d = V_{b2} - V_{b1}$

$$V_o = \frac{-\beta R_c V_d}{2(r_\pi + R_B)}$$

The differential-mode gain is

$$A_d = \frac{V_o}{V_d} = \frac{-QR_c}{2(r_\pi + R_B)}$$

The two input signals can be written as the sum of a differential-mode input signal component and a common-mode input signal component

$V_{b1}$  and  $V_{b2}$  in terms of  $V_d$  and  $V_{cm}$

$$V_{b1} = V_{cm} - \frac{\nu_d}{2} \qquad and \quad V_{b2} = V_{cm} - \frac{\nu_d}{2}$$

Substitute above values in equation 5

$$V_{o} = \frac{-\beta R_{C}}{r_{\pi} + R_{B}} \left\{ \frac{\binom{V}{cm} - \frac{v_{d}}{2} \left[ \left[ \frac{r_{\pi} + R_{B}}{(1+\beta)R_{o}} \right] + 1 \right] - \left( V_{cm} + \frac{v_{d}}{2} \right]}{\left[ \frac{r_{\pi} + R_{B}}{(1+\beta)R_{o}} \right] + 2} \right\}$$

$$V_{o} = \frac{-\beta R_{C}}{r_{\pi} + R_{B}} \{ \frac{V_{Cm} [[\frac{r_{\pi} + R_{B}}{(1+\beta)R_{o}}] + 1 - 1] - \frac{v}{2} [[\frac{r_{\pi} + R_{B}}{(1+\beta)R_{o}}] + 1 + 1]}{[\frac{r_{\pi} + R_{B}}{(1+\beta)R_{o}}] + 2} \}$$

$$V_{o} = -\frac{\beta R_{C}}{r_{\pi} + R_{B}} \left\{ \frac{V_{Cm} [[\frac{r_{\pi} \pm R_{B}}{(1+\beta)R_{o}}]] - \frac{v_{d}}{2} [[\frac{r_{\pi} \pm R_{B}}{(1+\beta)R_{o}}] + 2]}{[\frac{r_{\pi} \pm R_{B}}{(1+\beta)R_{o}}] + 2} \right\}$$

$$V_{o} = \frac{-\beta R_{C}}{r_{\pi} + R_{B}} \left\{ \frac{V_{Cm}[[\frac{r_{\pi} + R_{B}}{(1+\beta)R_{o}}]]}{[\frac{r_{\pi} + R_{B}}{(1+\beta)R_{o}}] + 2} - \frac{v_{d}[\frac{r_{\pi} + R_{B}}{(1+\beta)R_{o}}] + 2}{2[\frac{r_{\pi} + R_{B}}{(1+\beta)R_{o}}] + 2} \right\}$$

We can write the output voltage in the general form

$$V_o = A_{cm}V_{Cm} + A_dV_d \qquad ---7$$

Compare equations 6 and 7

$$A_{cm} = \frac{-QR_c}{(r_{\pi} + R_B) + 2(1 + Q)R_o} and A_d = \frac{QR_c}{(r_{\pi} + R_B)2}$$

The common-mode gain goes to zero for an ideal current source in which  $Ro = \infty$ .

#### For Two sided output (Balanced output)

$$V_o = V_{C2} - V_{C1}$$

The differential mode voltage gain is  $A_d = \frac{QR_c}{r_{\pi} + R_B}$  and the common-mode voltage gain is given by

# , $A_{cm} = 0$

**Common-Mode Rejection Ratio** (**CMRR**): The ability of a differential amplifier to reject a common-mode signal is described in terms of the common-mode rejection ratio (CMRR

The CMRR is a figure of merit for the diff-amp and is defined as

$$CMRR = \frac{A_d}{A_{cm}}$$

For an ideal diff-amp,  $A_{cm} = 0$  and  $CMRR = \infty$ .

Usually, the CMRR is expressed in decibels, as follows:

$$CMRR_{dB} = 20 \, \log_{10} \frac{A_d}{A_{cm}}$$

Form the differential amplifier analysis we can substitute the  $A_{cm}$  &  $A_d$  and CMRR Can be expressed as,

$$CMRR = \frac{A_d}{A_{cm}} = \frac{\frac{\beta R_C}{(r_{\pi} + R_B)^2}}{\frac{-\beta R_C}{(r_{\pi} + R_B) + 2(1 + \beta)R_o}}$$

$$CMRR = \frac{A_l}{A_{cm}} = \frac{1}{2} \frac{(r_{\pi} + R_B) + 2(1 + \beta)R_o}{(r_{\pi} + R_B)}$$

$$CMRR = \frac{A_d}{A_{cm}} = \frac{1}{2} [1 + \frac{2(1 + Q)R_o}{(r_{\pi} + R_B)}]$$

Determine the differential- and common-mode gains and the common mode rejection ratio of a diff-amp*V*+ = 10 V, *V*- = -10 V, *I*<sub>Q</sub> = 0.8 mA, and *R*<sub>C</sub> = 12 k. The transistor parameters are  $\beta$  = 100 and *R*<sub>o</sub> = 25 k. Assume the source resistors *R*<sub>B</sub> are zero. Use a one-sided output at *V*<sub>C2</sub>.

$$A_{d} = \frac{\beta R_{C}}{(r_{\pi} + R_{B})2} \qquad \therefore R_{B} = 0$$

$$A_{d} = \frac{g_{m}R_{C}}{2} \qquad \qquad \therefore g_{m}r_{\pi} = \beta$$

$$A_{d} = \frac{g_{m}R_{C}}{2} = \frac{\frac{I_{Q}}{2} \frac{R}{V_{T}}}{2 \frac{V_{T}}{V_{T}}} = \frac{\frac{I_{Q}}{2} \frac{R}{V_{T}}}{2 \frac{V_{T}}{V_{T}}} = \frac{\frac{I_{Q}}{2} \frac{R_{C}}{V_{T}}}{4 \frac{V_{T}}{V_{T}}} = \frac{(0.8)(12)}{4 (0.026)} = 92.3 \qquad \therefore V_{T} = 26 mv$$

$$A_{cm} = \frac{-\beta R_{C}}{(r_{\pi} + R_{B}) + 2(1 + \beta)R_{o}} = -0.237 \qquad \qquad \therefore r_{\pi} = \frac{\beta}{g_{m}}$$

$$CMRR = |\frac{A_{d}}{A_{cm}}| = |\frac{92.3}{-0.237}| = 389$$

$CMRR_{dB} = 20 \log_{10} CMRR = 20 \log_{10} 389 = 51.8 \, dB$

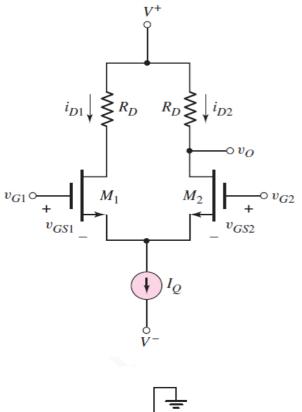

## **MOSFET Differential Amplifier:**

- The basic MOSFET differential pair, with matched transistors  $M_1$  and  $M_2$  biased with a constant current  $I_Q$ .

- Assume that  $M_1$  and  $M_2$  are always biased in the saturation region.

- Even with  $v_{G1} = v_{G2} = 0$ , the transistors  $M_1$ and  $M_2$  can be biased in the saturation region by the current source  $I_Q$ .

This is a DC coupled diff amplifier

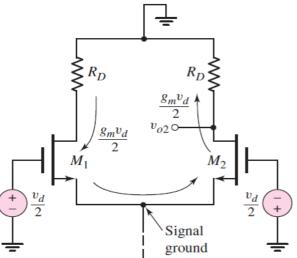

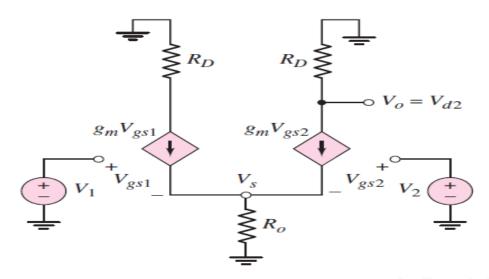

The ac equivalent circuit of the diff-amp configuration, Shown in fig.

One sided output voltage is:

$$V_O = V_{o2} = \left[\frac{g_m V_d}{2}\right] R_D$$

$$A_d = \frac{V_o}{V_d} = \frac{g_m R_D}{2}$$

FigureAC equivalent circuit,MOSFET differential amplifier

Assuming the Transistors are identical in all parameters.  $(g_{m1}=g_{m2}=g_m)$

Apply KCL at node V<sub>s</sub>

$$g_m V_{gs1} + g_n V_{gs2} = \frac{V_s}{R_o} ---1$$

From the circuit  $V_{gs1} = V_1 - V_s$  and  $V_{gs2} = V_2 - V_s$

Substitute above values in equation 1

$$g_{m}(V_{1} - V_{s}) + g_{m}(V_{2} - V_{s}) = \frac{V_{s}}{R_{o}}$$

$$g_{m}(V_{1} + V_{2} - 2V_{s}) = \frac{V_{s}}{R_{o}}$$

$$(V_{1} + V_{2} - 2V_{s}) = \frac{V_{s}}{g_{m}R_{o}}$$

$$(V_{1} + V_{2}) = \frac{V_{s}}{g_{m}R_{o}} + 2V_{s}$$

$$(V_{1} + V_{2}) = V_{s}(2 + \frac{1}{g_{m}R_{o}})$$

$$V_{s} = \frac{(V_{1} + V_{2})}{(2 + \frac{1}{g_{m}R_{o}})}$$

For a one-sided output at the drain of  $M_2$

----2

Substitute equation 2 in equation 3

$$V_{o} = -g_{m}R_{D} \left[ V_{2} - \frac{(V_{1} + V_{2})}{(2 + \frac{1}{g_{m}R_{0}})} \right]$$

$$V_{o} = -g_{m}R_{D} \left[ \frac{V_{2}(2 + \frac{1}{g_{m}R_{0}}) - V_{1} - V_{2}}{(2 + \frac{1}{g_{m}R_{0}})} \right]$$

$$V_{o} = -g_{m}R_{D} \left[ \frac{V_{2}(2 + \frac{1}{g_{m}R_{0}} - 1) - V_{1}}{(2 + \frac{1}{g_{m}R_{0}})} \right]$$

$$V_{o} = -g_{m}R_{D} \left[ \frac{V_{2}(2 + \frac{1}{g_{m}R_{0}}) - V_{1}}{(2 + \frac{1}{g_{m}R_{0}})} \right]$$

$V_{b1}$  and  $V_{b2}$  in terms of  $V_d$  and  $V_{cm}$

$$V_1 = V_{cm} - \frac{v_d}{2} \qquad and \quad V_2 = V_{cm} - \frac{v_d}{2}$$

Substitute above values in equation 4

$$V_{0} = -g_{m}R_{D}\left[\frac{(V_{cm} - \frac{v}{2})(1 + \frac{1}{g_{m}R_{0}}) + V_{cm} + \frac{v}{2}}{(2 + \frac{1}{g_{m}R_{0}})}\right]$$

$$V_{0} = -g_{m}R_{D}\left[\frac{V_{cm}(1 + \frac{1}{g_{m}R_{0}} - 1) - \frac{v}{2}(1 + \frac{1}{g_{m}R_{0}} + 1)}{(2 + \frac{1}{g_{m}R_{0}})}\right]$$

$$V_{0} = -g_{m}R_{D}\left[\frac{V_{cm}(-\frac{1}{g_{m}R_{0}}) - \frac{v}{2}(2 + \frac{1}{g_{m}R_{0}})}{(2 + \frac{1}{g_{m}R_{0}})}\right]$$

$$V_{0} = -g_{m}R_{D}\left[\frac{(\frac{1}{g_{m}R_{0}})}{(2 + \frac{1}{g_{m}R_{0}})}\right]V_{cm} + \frac{g_{m}R_{D}}{2}\left[\frac{(2 + \frac{1}{g_{m}R_{0}})}{(2 + \frac{1}{g_{m}R_{0}})}\right]v_{d}$$

$$V_{0} = -g_{m}R_{D}\left[\frac{(\frac{1}{2} - \frac{1}{g_{m}R_{0}})}{(2 - \frac{1}{g_{m}R_{0}})}\right]V_{cm} + \frac{g_{m}R_{D}}{2}\left[\frac{(2 + \frac{1}{g_{m}R_{0}})}{(2 + \frac{1}{g_{m}R_{0}})}\right]v_{d}$$

$$---5$$

We can write the output voltage in the general form

$$V_o = A_{cm}V_{cm} + A_dV_d \qquad ---6$$

Compare equations 5 & 6

$$A_d = \frac{g_m R_D}{2} \text{ and } A_{cm} = \begin{bmatrix} -g_m R_D \\ 2g_m & R \end{bmatrix}$$

The Transconductance

$$g_m$$

of the MOSFET is  $2\sqrt{\frac{K+1}{nDQ}} = \sqrt{\frac{2K+1}{nQ}}$   $\therefore I_{DQ} = \frac{l_Q}{2}$

Or  $g_m = \frac{2ID}{V_{gs}-V_t} = \frac{2\frac{l_Q}{2}}{V_{ov}} = \frac{l_Q}{V_{ov}}$   $\therefore V_{ov} = V_{ov} = V_t$

$A_d = \frac{g_m R_D}{2} = \sqrt{\frac{2K+1}{nQ}} = \sqrt{\frac{K_n IQ}{2}} R_D$

$A_{cm} = \left[\frac{-g_m R_D}{2g_m R_{o}+1}\right] = \left[\frac{-\sqrt{2K_n IQ} R_D}{2\sqrt{2K_n IQ} R_{o}+1}\right]$   $A_{cm} = 0$ ; when Ro =  $\infty$ . (Ideal Source)

$CMRR = \left|\frac{A_d}{A_{cm}}\right| = \frac{\sqrt{\frac{2}{2K_n IQ} R_D}}{\frac{\sqrt{2K_n IQ} R_D}{2\sqrt{2K_n IQ} R_{o}+1}} = \frac{1}{2}\frac{\sqrt{2K_n IQ} R_D [1+2\sqrt{2K_n IQ} R_O]}{\sqrt{2K_n IQ} R_D}$

$CMRR = \left|\frac{A_d}{A_{cm}}\right| = \frac{1}{2}\left[1 + 2\sqrt{2K_n IQ} R_D\right]$

For Two-Sided Output (Balanced Output):

$$A_d = g_m R_D$$

and  $A_{cm} = 0$

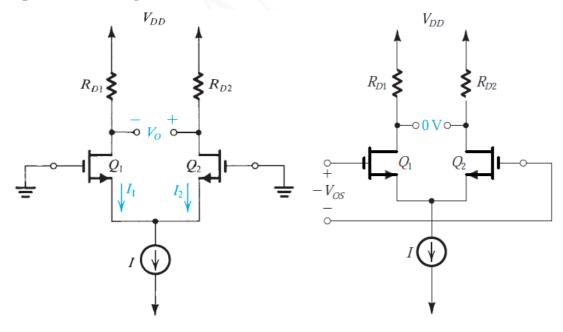

# Other Nonideal Characteristics of the Differential Amplifier

1. Input Offset Voltage of the MOS Differential Pair:

Fig.(a) both inputs grounded

Fig.(b) Vos applied at inputs

- Consider the basic MOS differential amplifier with both inputs grounded, as shown in Fig. (a).

- If the two sides of the differential pair were perfectly matched, then current I would split equally between Q<sub>1</sub> and Q<sub>2</sub>, and V<sub>0</sub> would be zero.

- But practical circuits exhibit mismatches that result in a dc output voltage V<sub>0</sub> even with both inputs grounded and is called output offset dc voltage.

- > Input Offset Voltage V<sub>os</sub> is that voltage which must be applied at the input to make output Offset Voltage zero.  $Vos = V_0/A_d$

- > The offset voltage is a result of device mismatches, its polarity is not known a priori.

- > Three factors contribute to the dc offset voltage of the MOS differential pair:

- Mismatch in load resistances,

- Mismatch in W/L,

- Mismatch in V<sub>t</sub>.

- Consider the three contributing factors one at a time.

Consider first the case where  $Q_1$  and  $Q_2$  are perfectly matched but  $R_{D1}$  and  $R_{D2}$  show a mismatch  $\Delta R_D$

$$R_{D1} = R_D + \frac{\Delta R_D}{2}$$

and  $R_{D2} = R_D - \frac{\Delta R_D}{2}$

Because  $Q_1$  and  $Q_2$  are matched, the current I will split equally between them. Because of the mismatch in load resistances, the output voltages  $V_{D1}$  and  $V_{D2}$  will be

$$V_{D1} = V_{DD} - \frac{I}{2} \left( R_D + \frac{\Delta R_D}{2} \right)$$

$$V_{D2} = V_{DD} - \frac{I}{2} \left( R_D - \frac{\Delta R_D}{2} \right)$$

$$V_o = V_{D2} - V_{D1} = V_{DD} - \frac{I}{2} \left( R_D + \frac{\Delta R_D}{2} \right) - \left( V_{DD} - \frac{I}{2} \left( R_D - \frac{\Delta R_D}{2} \right) \right) = \frac{I}{2} \Delta R_D$$

Input offset voltage is obtained by dividing  $V_0$  by the gain  $g_m R_D$

Thus the offset voltage is directly proportional to V<sub>OV</sub>. Let V<sub>OV</sub> =0.2V and the worst case mismatch will be  $\Delta R_D/R_D = 0.02$ . The resulting input offset voltage will be  $|V_{0S}| = 0.1X \ 0.02 = 2mV$ .

Similarly  $V_{\sigma}$  due to mismatch in  $\frac{W}{L}$

$$V_{s} = \binom{V_{ov}}{2} \begin{pmatrix} \Delta \frac{W}{L} \\ \frac{W}{L} \end{pmatrix}$$

Similarly  $V_{os}$  due to mismatch in  $V_{ds}$

$$V_{os} = \Delta V_t$$

Total input offset voltage can be found as

$$V_{os} = \sqrt{\left(\left(\frac{ov}{2}\right)\left(\frac{\Delta R}{R_{0}}\right)^{2} + \left(\left(\frac{V_{ov}}{2}\right)\left(\frac{\Delta W}{L}\right)\right)^{2} + (\Delta V_{t})^{2}}$$

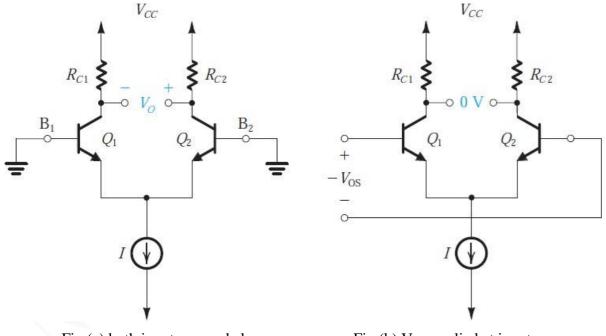

Input Offset Voltage of the Bipolar Differential Amplifier:

Fig.(a) both inputs grounded

Fig.(b) Vos applied at inputs

Here the output offset results from mismatches in the load resistances in the load resistance  $R_{c1}$  and  $R_{c2}$  and from junction area,  $\beta$ , and other mismatches in  $Q_1$  and  $Q_2$

Consider first the effect of the load mismatch

$$R_{c1} = R_c + \frac{\Delta R_c}{2}$$

and  $R_{c2} = R_c - \frac{\Delta R}{2}$

Assume that  $Q_1$  and  $Q_2$  are perfectly matched. The current I will be divide between  $Q_1$  and  $Q_2$ , and thus

$$V_{c1} = V_{cc} - \frac{\alpha I}{(2)} \left( R_c + \frac{\Delta R}{2} \right) and V_{c2} = V_{cc} - \frac{\alpha I}{(2)} \left( R_c - \frac{\Delta R_c}{2} \right)$$

$$V_{o} = V_{c2} - V_{c1} = V_{cc} - \frac{\alpha I}{(2)} \left( R_{c} - \frac{\Delta R}{2} \right) - \left( V_{cc} - \left( \frac{\alpha I}{2} \right) \left( R_{c} + \frac{\Delta R}{2} \right) \right) = \left( \frac{\alpha I}{2} \right) \Delta R_{c}$$

Input offset voltage is obtained by dividing  $V_0$  by the gain  $g_m R_D$

Here the offset voltage is proportional to  $V_T$  and  $V_T = 25 \ mV$ . The worst case mismatch will be  $\Delta R_D/R_D = 0.02$ . The resulting input offset voltage will be  $|V_{0S}| = 25 \ X \ 0.02 = 0.5 \ mV$ .

Let the transistor have a mismatch in their emitter-base junction areas. Such an area mismatch gives rise to a proportional mismatch in the scale currents  $I_s$ . Similarly  $V_{os}$  due to mismatch in  $I_s$

$$V_{os} = V_T \left(\frac{\Delta I_S}{I_S}\right)$$

Total input offset voltage can be found as

$$V_{os} = \sqrt{\left(\frac{\Delta R_c}{R_c}\right)^2 + \left(V_T \left(\frac{\Delta I_S}{I_S}\right)\right)^2}$$

$$V_{os} = V_T \sqrt{\left(\frac{\Delta R_c}{R_c}\right)^2 + \left(\frac{\Delta I_S}{I_S}\right)^2}$$

#### Input Bias and Offset Currents of the Bipolar Differential Amplifier:

> In a perfectly symmetric differential pair the two input terminals carry equal dc currents; that

is,

$$I_{B1} = I_{B2} = \frac{I/2}{1+Q}$$

This is the input bias current of the differential amplifier. Mismatches in the amplifier circuit like a mismatch in β make the two input dc currents unequal. The resulting difference is the input offset current, I<sub>OS</sub>, given as

$$Ios = |I_{B1} - I_{B2}|$$

Let

$$Q_{I} = Q + \frac{\Delta Q}{2}$$

and  $Q_{I} = Q - \frac{\Delta Q}{2}$

Then  $I_{B1} = \frac{I}{2} \frac{1}{1+\beta+\frac{\Delta\beta}{2}}$  and  $I_{B2} = \frac{I}{2} \frac{1}{1+\beta-\frac{\Delta\beta}{2}}$

$$Ios = |I_{B1} - I_{B2}| = \frac{I}{2(1+Q)} \left(\frac{\Delta Q}{Q}\right)$$

Formally input bias current  $I_B$  is defined as

$$I_{B} = \frac{I_{B1} + I_{B2}}{2} = \frac{I}{2(1+Q)}$$

$$I_{OS} = |I_{B1} - I_{B2}| = I_{B} \left(\frac{\Delta Q}{Q}\right)$$

For example, a 10%  $\beta$  mismatch results in an offset current that is one-tenth the value of the input bias current.

Finally note that a great advantage of the MOS differential pair is that it does not suffer from a finite input bias current or from mismatches.