## **FACULTY OF ENGINEERING**

B.E. 3/4 (ECE) I – Semester (New) (Suppl) Examination, May 2013

**Subject : Digital Integrated Circuits and Applications**

Time: 3 hours Max. Marks: 75

Note: Answer all questions from Part-A and answer any FIVE questions from Part-B.

## PART – A (25 Marks)

| PART – A (25 Marks)                                                                                                                                                                   |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1. Draw the circuit of three input TTL NAND gate.                                                                                                                                     | 2        |

| 2. Write the description of i) 74 HC 00 ii) 74 ALS 86 iii) 74 LS 83 iv) 74 S 85                                                                                                       | 3        |

| 3. Write any two advantages and disadvantages of CMOS logic.                                                                                                                          | 2        |

| 4. Explain briefly about the function generator using ROM.                                                                                                                            | 3        |

| 5. Implement the Demultiplexer by using 74ALS138.                                                                                                                                     | 2        |

| <ol><li>Classify the types of seven segment displays and write the importance of LT, BI/RB0<br/>RBI inputs.</li></ol>                                                                 | O,<br>3  |

| 7. Implement the sum & carry outputs of a full adder using 4 : 1 MUX.                                                                                                                 | 3        |

| 8. Draw the mod 8 asynchronous down counter and draw its timing diagram.                                                                                                              | 3        |

| 9. A certain memory is specified as 4K x 32. How many words can be stored on the chand what is the capacity of the memory system?                                                     | nip<br>2 |

| 10. Define the term mask-programmable and give an example.                                                                                                                            | 2        |

| PART – B (50 Marks)                                                                                                                                                                   |          |

| 11.a) A two input NAND gate has $V_{cc}$ = +5v and 1 K $\Omega$ load connected to its output. Calculate the output voltage i) when both inputs are low ii) when both inputs are HIGH. | 5        |

| <ul> <li>b) Explain IC interfacing techniques for CMOS to TTL logic families and TTL to<br/>CMOS logic families.</li> </ul>                                                           | 5        |

| 12.a) Draw the circuit diagram of a 2 input ECL NOR/OR gate and explain its operation with the truth tables.                                                                          | າ<br>5   |

| <ul><li>b) Compare the following technologies.</li><li>i) TTL and CMOS</li><li>ii) TTL and ECL</li></ul>                                                                              | 5        |

| 13.a) Explain the operation of 3 bit presettable counter and the operation of 74 LS 193 Counter.                                                                                      | 5        |

|                                                                                                                                                                                       |          |

5

5

5

5

5

5

5

- 14.a) Explain parallel, serial and carry look ahead adder with its circuit diagrams.

- b) Realise the binary subtractor with 2's complement circuit with 74 LS 83 to get the true magnitude output for all combinations.

- 15.a) Compare PAL, PROM and PLA with the help of block schematics and explain the respective advantages.

- b) Implement the following functions by using PROM, PLA, PAL

$$f_1(a, b,c) = \sum m (0, 1, 3, 6, 7)$$

$f_2(a, b,c) = \sum m (2, 3, 4, 5)$

$f_3(a, b,c) = \sum m (0, 1, 2, 3, 4, 5, 6, 7)$

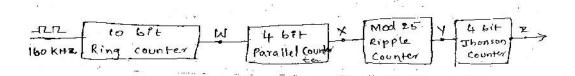

16.a) Determine the frequency of pulses at points w, x, y, and z in the circuit.

- b) Design a melay type sequence detector to defect a serial input sequence of 101. 5

- 17. Write a short notes on any two of the following:

- b) Expanding word size and capacity

- c) Johnson and Ring counters

\*\*\*\*\*